# Data Communication On Electric Line

Cherdchai Jungsathitkul (361 - 6310)

# **Data Communication On Electric Line**

Presented To Dr. Pharon Sanguanbhokai

#### BY

Cherdchai Jungsathitkul (361-6310)

Suvir Kumar (361-6898)

This project is a part of the requirement of the courses EN4902 and EE4902 Electronics and Electrical Engineering Project II

> **Faculty Of Electronics Engineering Faculty Of Electrical Engineering**

> > ABAC School Of Engineering Assumption University March 16<sup>th</sup>, 1998

#### **Table of Contents**

| Acknowledgment | 1 |

|----------------|---|

| Abstract       | 5 |

## **Chapter 1 Introduction**

| Introduction To Power Line Communication             | 9   |

|------------------------------------------------------|-----|

| Short Description Of Project                         | 10  |

| Main Block Diagram                                   | .11 |

| Summary Of Various Parts Of The Block Diagram        |     |

| Existing Power Line Communications Standards         | 12  |

| Forecasted Problems Using The Carrier Current System | 12  |

| UNITEDITY                                            |     |

|                                                      |     |

# Chapter 2 Theory & Design

| The PC Parallel Port.                                 | 14 |

|-------------------------------------------------------|----|

| Introduction and Background of Parallel Ports         | 14 |

| Brief History On The Development Of The Parallel Port | 15 |

| Hardware Properties                                   | 15 |

| Address Notes                                         | 17 |

| Start Address Function                                |    |

| Modulation and Demodulation                           |    |

| FSK Modulation Theory                                 | 19 |

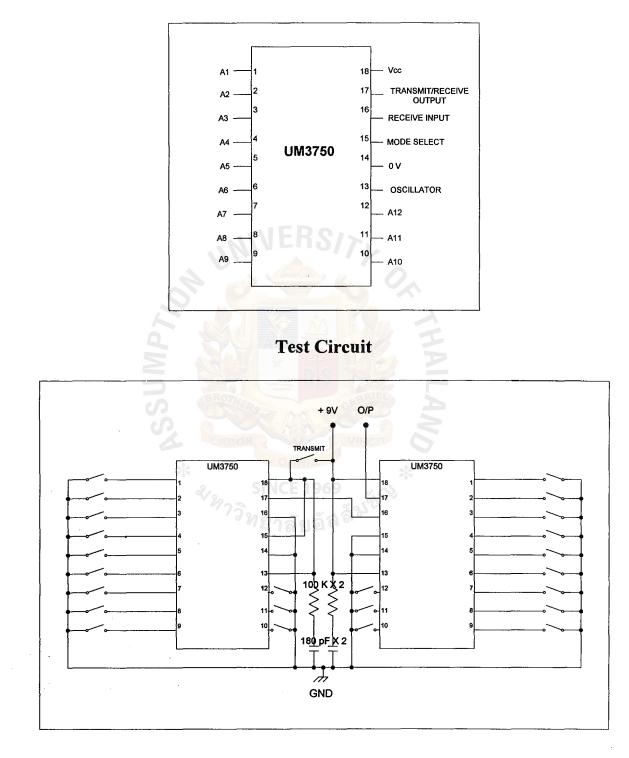

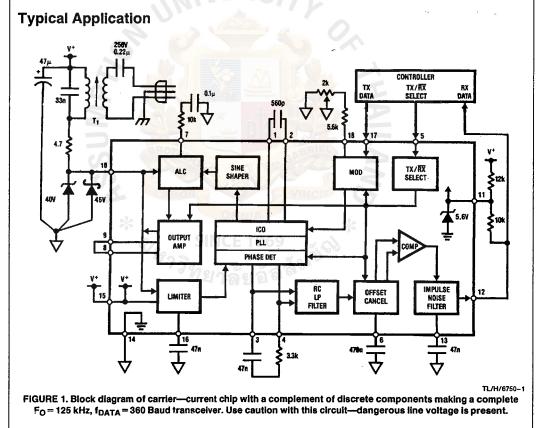

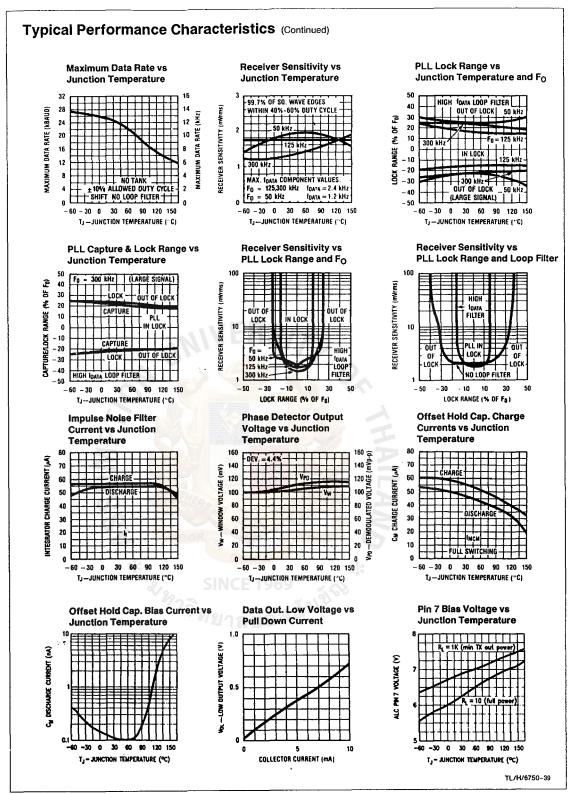

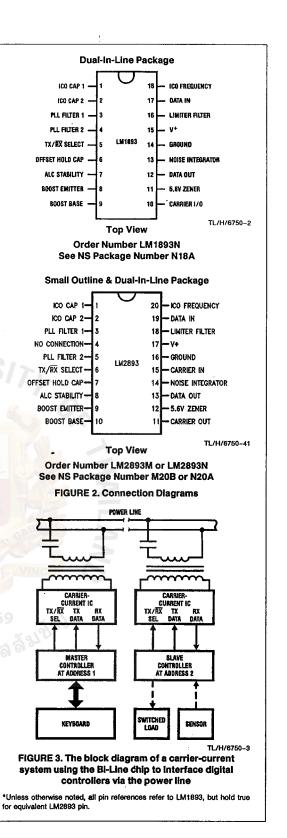

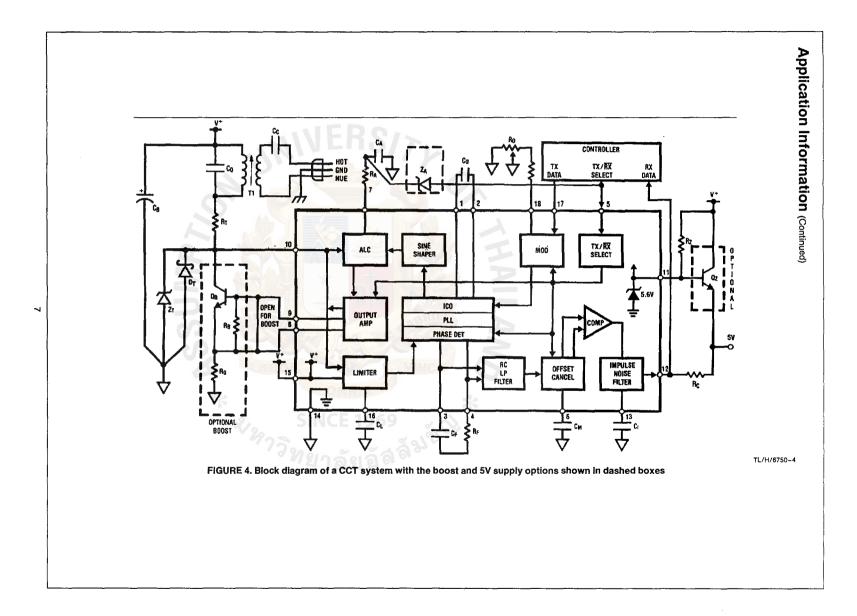

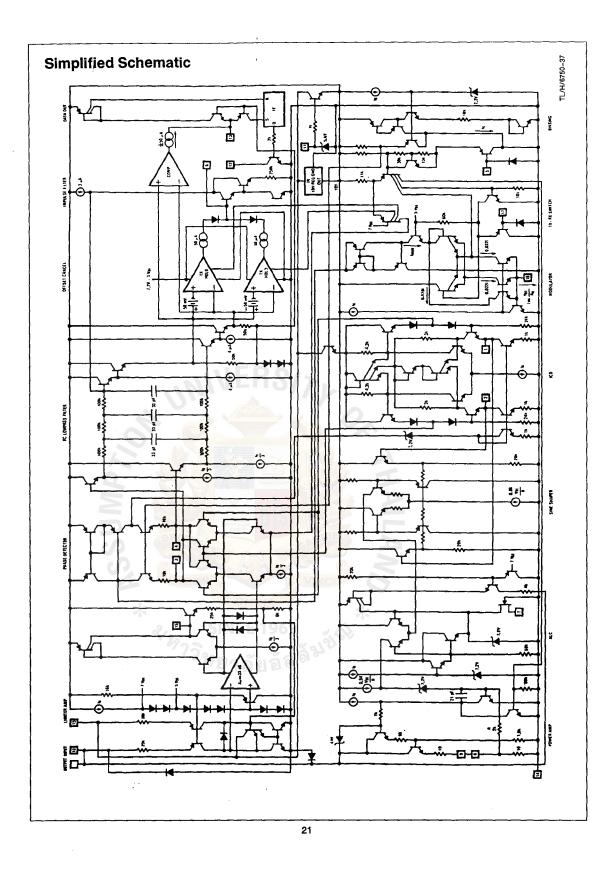

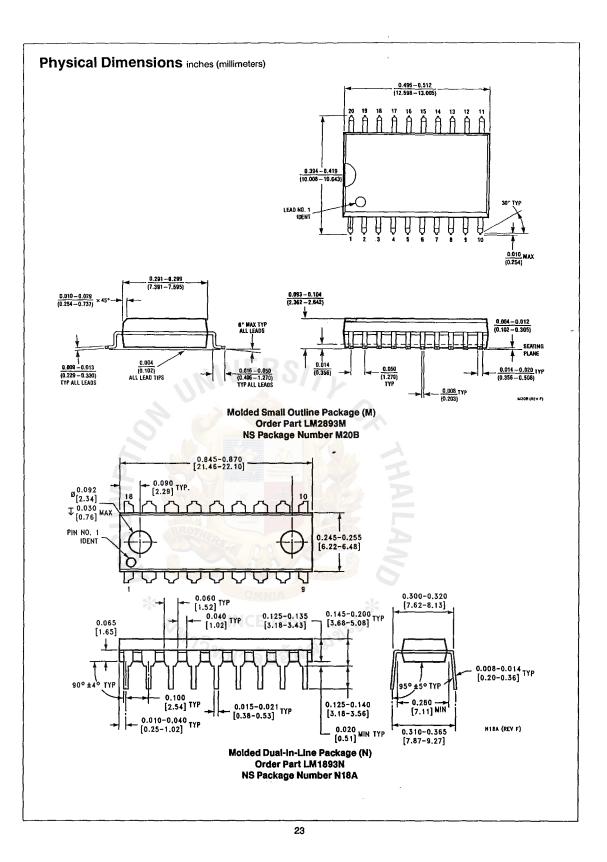

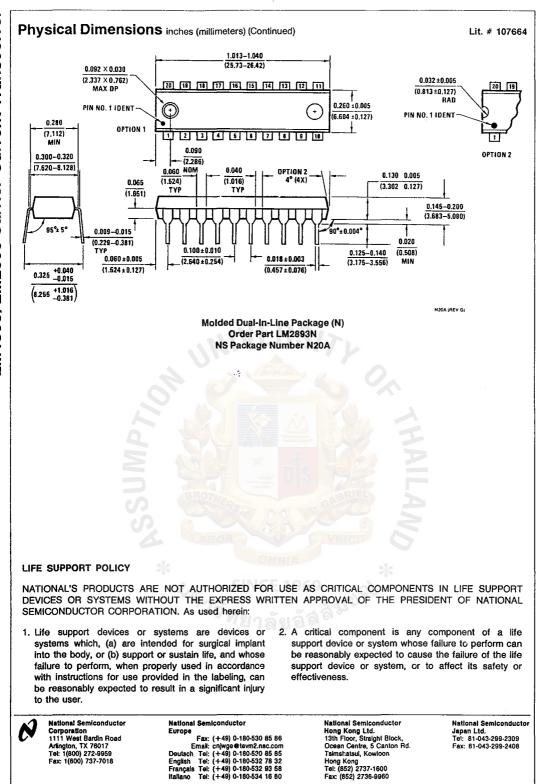

| Theory of LM1893SINCE 1969                            | 22 |

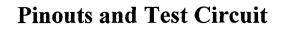

| Theory of UM3750 Decoder / Encoder Chip               | 23 |

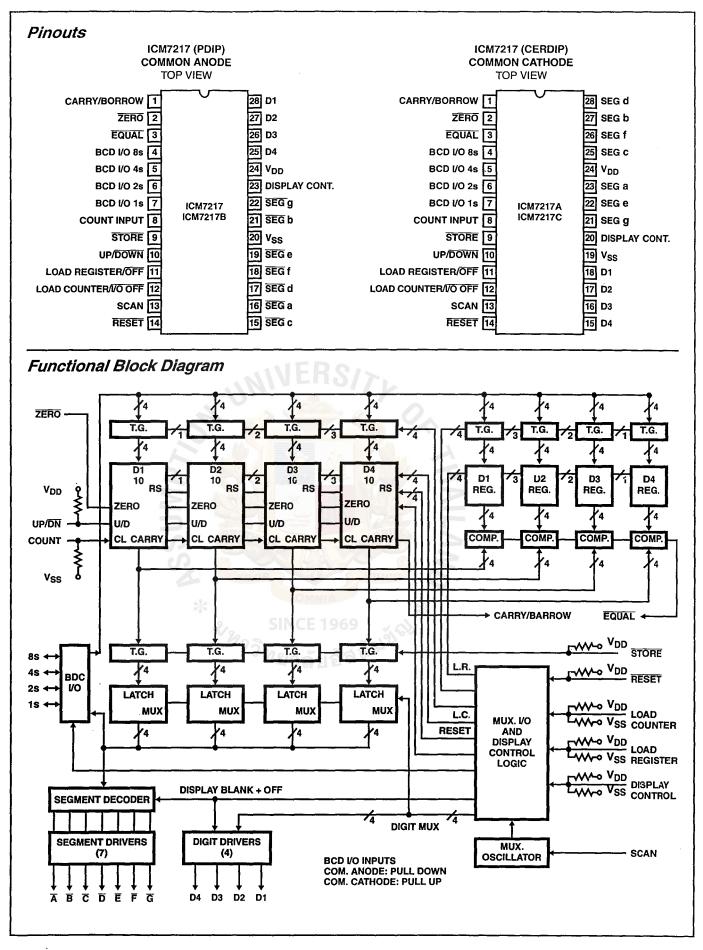

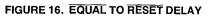

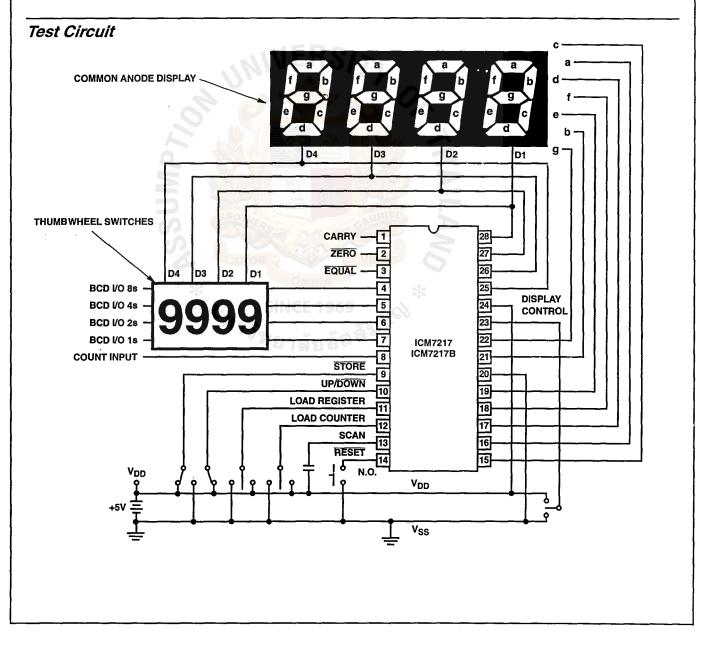

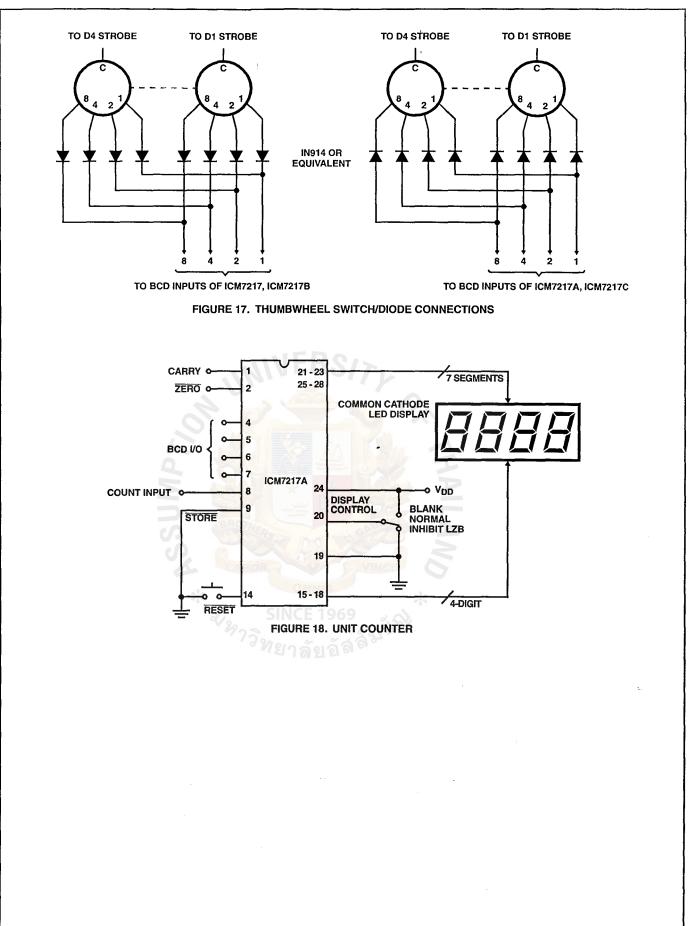

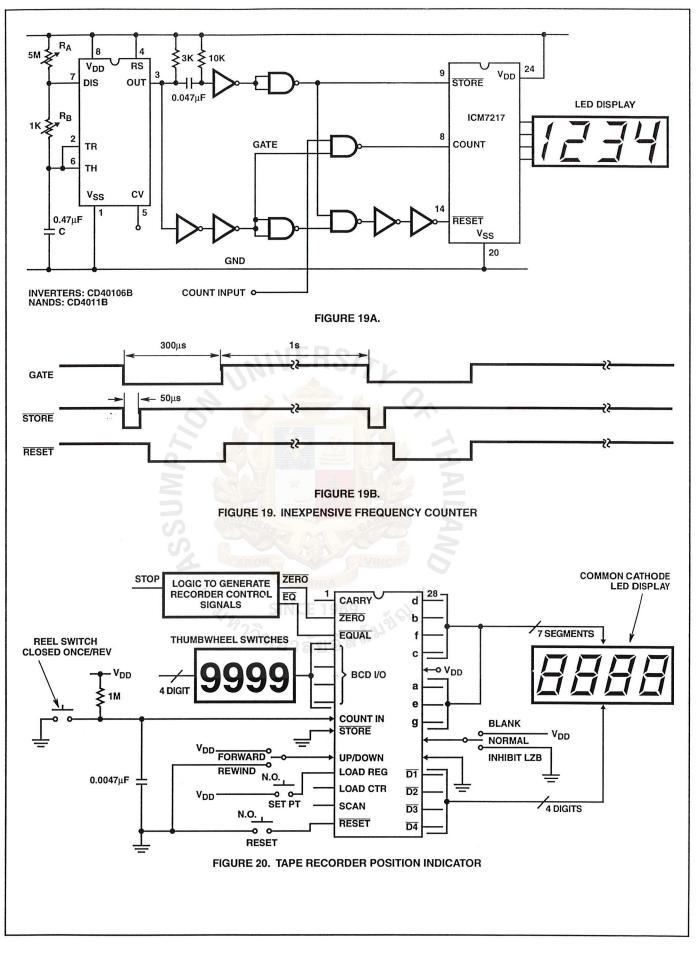

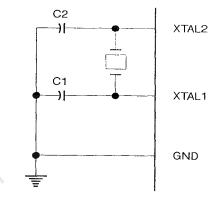

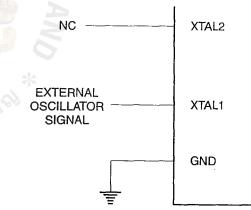

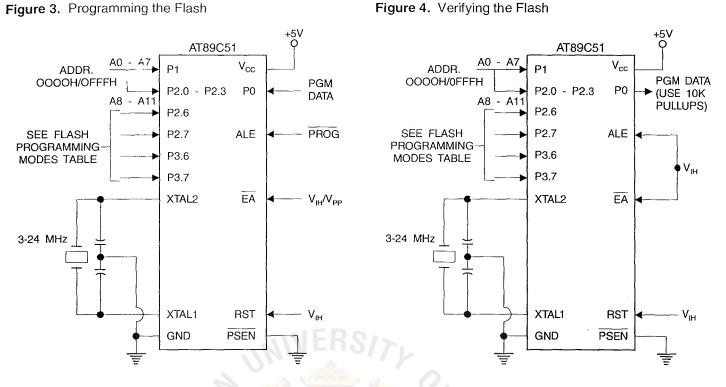

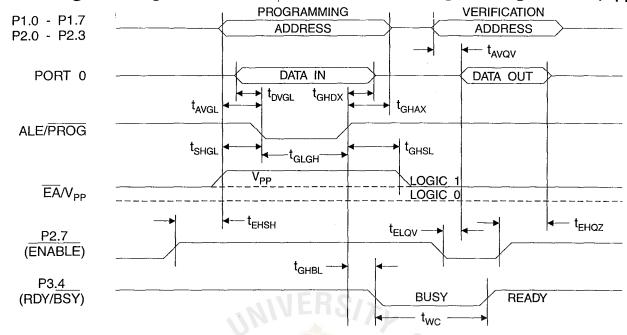

| Theory of Microcontroller Timer and Display           | 24 |

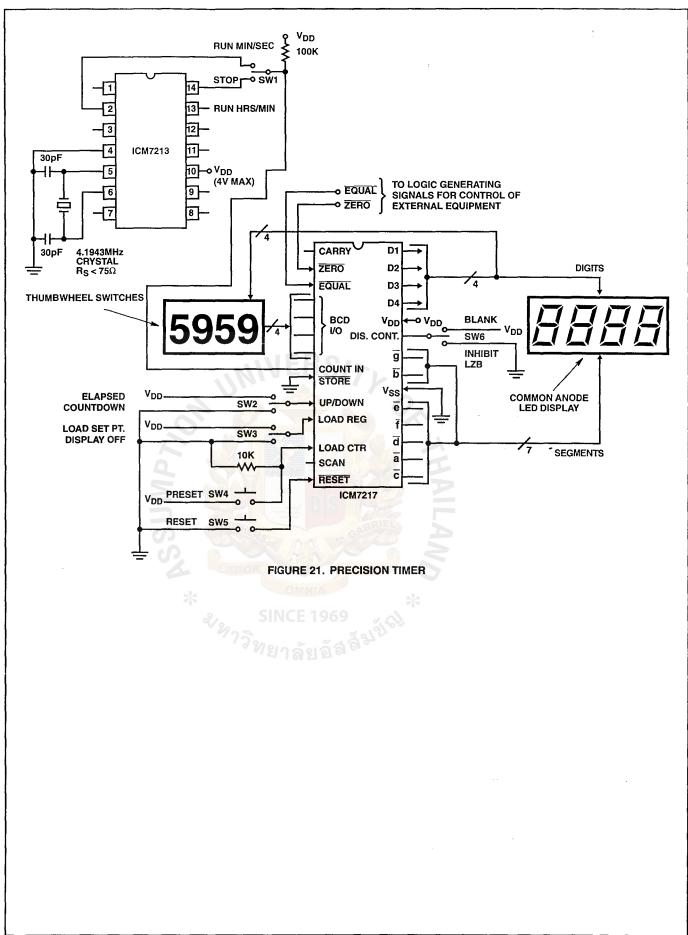

| Timer Circuit Description                             | 27 |

|                                                       |    |

## **Chapter 3 Fabrication & Construction**

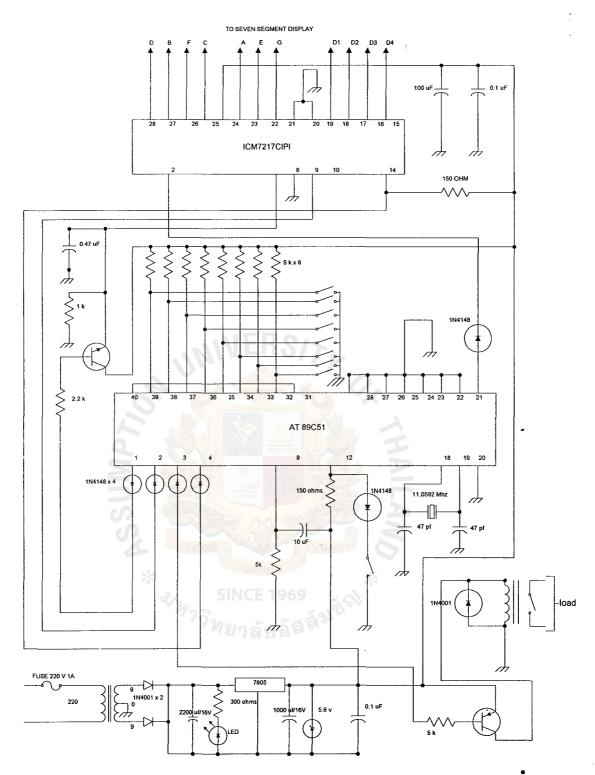

| Schematic Diagram | AT89C51 and ICM7217 Unit | 30 |

|-------------------|--------------------------|----|

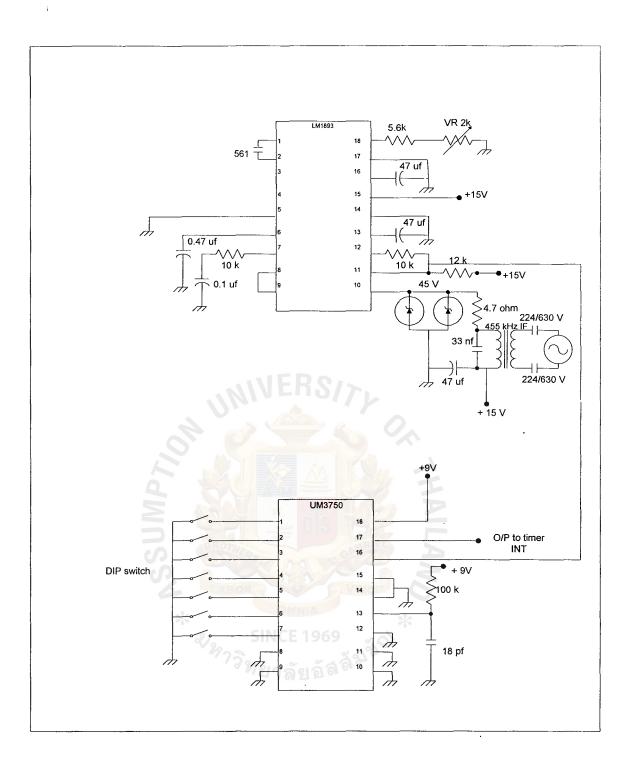

| Schematic Diagram | Receiver                 | 31 |

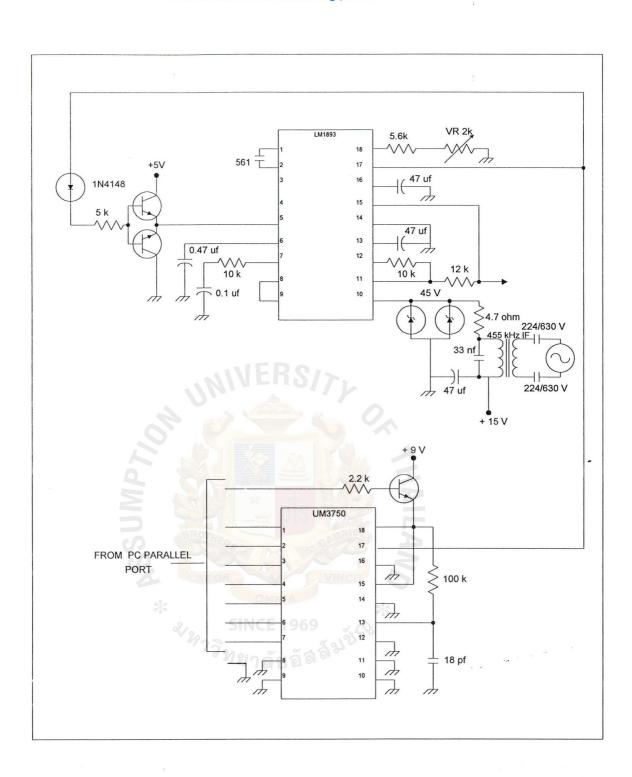

| Schematic Diagram | Transmitter              | 32 |

#### Chapter 4 Program Source Codes

| Pascal & The PC Parallel Port | 33 |

|-------------------------------|----|

| Foxpro Program Source Code    | 33 |

| AT89C51 Assembly Program      | 62 |

#### **Chapter 5 Test Experiments, Equipment**

| First Experimental Tests                     | 67 |

|----------------------------------------------|----|

| Equipment Used In Experiment and Fabrication | 69 |

| Electronic Component Used                    | 70 |

#### **Chapter 6 Conclusion & Recommendation**

| Conclusion     | 71 |

|----------------|----|

| Recommendation | 72 |

# Project Information .

| Bibliographies & References                          | 73 |

|------------------------------------------------------|----|

| Vita & Photograph Suvir Kumar (361-6898)             |    |

| Vita & Photograph Cherdchai Jungsathitkul (361-6310) |    |

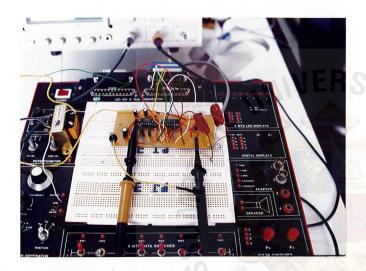

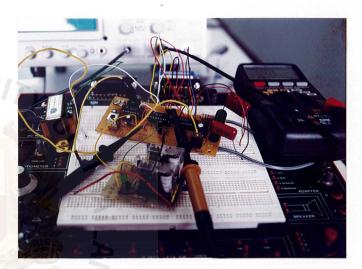

| Project Photographs                                  |    |

# Appendix

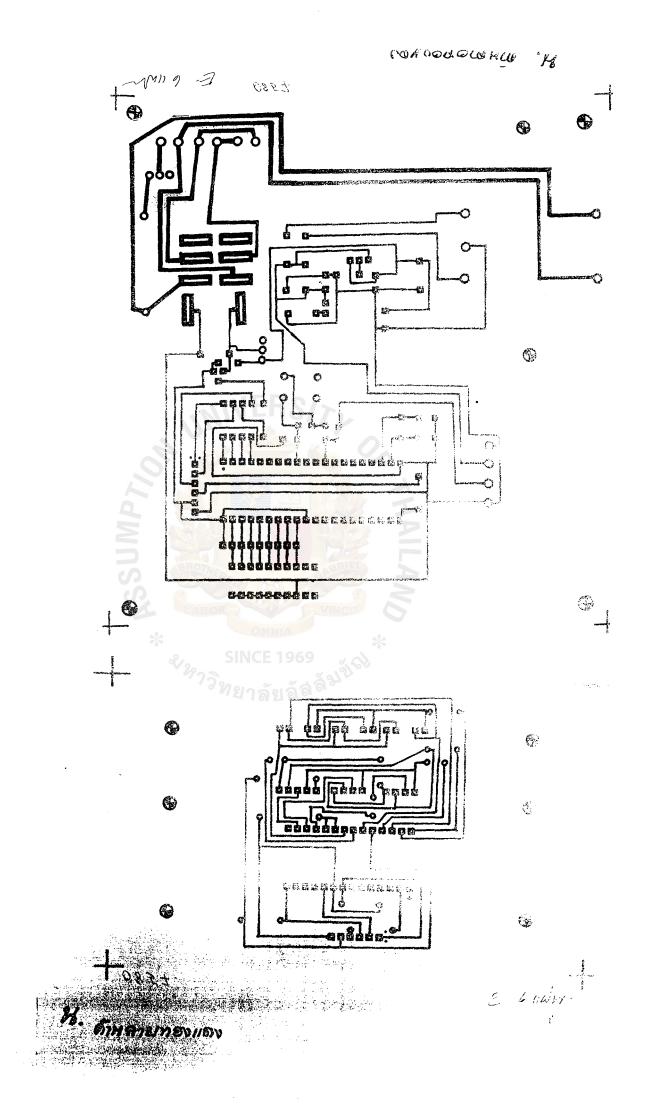

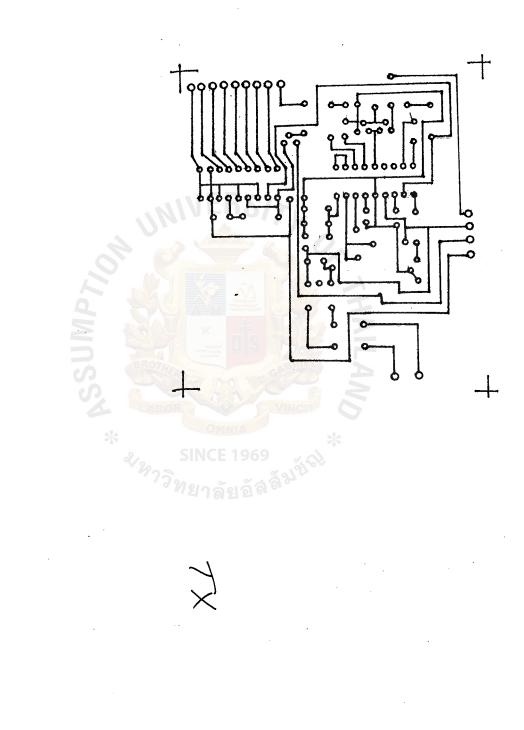

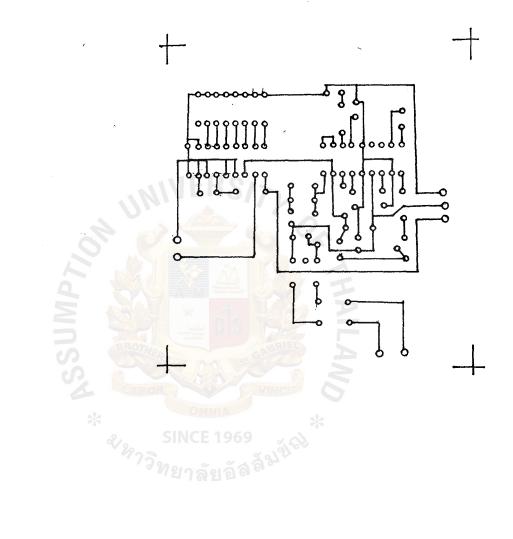

PCB Foil Pattern Microcontroller Based Timer PCB Foil Pattern Rx and Tx Modules Data Sheet UM 3750 Encoder/Decoder Data Sheet AT89C51 Data Sheet LM1893N Data Sheet ICM71217

#### Acknowledgment

This project is a part of the requirement of the course EN4902 and EE4901 (Electronics and Electrical Engineering Project II) as required by the Faculty of Engineering Assumption University. This project report is a compilation of data from many sources such as projects of others whom have graduated before us, many textbooks, various web sites, data sheets downloaded from the internet and most important of all our knowledge which we have gained here at Assumption University as a result of our years of professional training here.

Our project is a combination of the suggestions and previous works of those whom we consider our Mentors. This is our chance to acknowledge others for their great influence and contribution. We must thank particularly, Dr. Pharon Sanguanbhokai our project adviser, who suggested many topics on which we could work on and how to go about working and researching on each particular project. We would also like to thank Dr. Win Tin and Dr. Seshanna for opening our eyes to the interesting modern world of Electronics and Microprocessors. We would also like to thank all our other instructors for all the knowledge that they have passed on to us which has enabled us to come this far in the academic world.

We would like to thank The President of Assumption University Brother Martin for without his great management skills Assumption University would not be half of what it is today. The Dean Of The Faculty Of Engineering and Associate Dean Of The Faculty Of Engineering Dr. Suttiporn and Dr. Win Tin for their support and funding for the Network Research Center where we used all the tools and equipment in the fabrication of our project.

Thank you Rodney Simon (362-6105) for the great data books from National Semiconductor. Zaw Tin Oo for the knowledge of using the LM1893 Carrier Current transceiver and your advice in using Pascal Language for the control of The PC Parallel Port. Poltat Sirvattanalak for his help in designing the foil pattern of our Printed Circuit Board and helping our with the drilling, soldering, spray painting and all other labour intensive jobs that were a part of building up this project. Lester Protacio (362-1871) for his help and advice in the use of Microsoft Word and organizing this project report. Ursa Major International for their generous supply of reporting resources and the use of their Laser Printer. Thank you Pittaya Achriyasilp of Siam Hardware Industry for your generous loan of a Laptop Computer that was required in the Demonstration of this project which will take place in front of the Project Committee Office of The Faculty of Engineering Assumption University. Thank you Malcolm C. Rubel for your wonderful book Title Foxpro Power Tools. Thank you for making Foxpro programming so easy!

We would also like to take this opportunity to thank all our friends those future Engineers who gave us advice and new ideas. Lastly, we would like to say that Aunet is really a hopeless Internet Service Provider. Aunet you have all the equipment, all the phone lines, all the latest equipment but you don't bother maintaining it, what good is that? Change your attitude and improve your service, AuNet!

#### Abstract

In this present day of high technology and competition we must be more productive and cost conscious. The projects which we design as Electrical and Electronic Engineers must be cheaper and more efficient. With less time on our hands because of our busy schedules new products must be designed to be easier to use than ever before. More than that these products must be easy to install, upgrade and repair. The ideal system should be able to be broken into many small identical pieces, so that in the event of a failure in some part of the system, replacements can be made almost instantly.

AC Electric line medium Technically using the as а of called The Current Carrier communication is System. Our Computerized remote control system using the Carrier Current System as a medium is a very efficient way of controlling electronic and electrical devices within a local area that utilizes the same mains transformer. The advantages and disadvantages of this type of system will be discussed later in this project. We will use the FSK method of modulation because it is less error prone, in a noisy environment such as the Electric line.

This device can be used to build your own home, office or factory automation system where you can control lights, relays, timers and other transducers in your environment. Turn things on/off or control devices like stereos, etc. This project is Uni-Directional. It utilises Open Loop Control because of its simplicity and reasons due to lack of funding and time. Below is a short list of some doable things with this type of system. Just to spark your imagination...some example applications are

- Control lights and other devices

- Security systems

- Energy control and management

- Process control

- Environmental control

- Heating and air condition control

- Sprinkler/watering systems

- Connect your whole home to Internet

- Help for elderly and disabled people

- Close blinds if sunlight is to strong

- Let your PC control your home

- Stage control in home theatres

There are many advantages of using the carrier current system as a system of communication. Once a node is configured using a simple, software driven process, it is instantly connected to the network and no further technical intervention is required. Users and non-technical personnel can move a node almost anywhere it is needed, even outdoors or into other environments where traditional cabled networks will not go.

The carrier current communication system is a network administrators dream. It's completely transparent in it's operation, and there is no added administration or support required.

When the carrier current system of communication is compared to other communication systems it stands out with the following advantages...

- It eliminates cabling and construction costs.

- It's connections requires only minutes to install.

-17

- It does not require added cost hubs or antennae.

- It does not require master stations or special ISA/PCMCIA cards.

- It does not disrupt staff or necessitate facility rearrangement.

- No special cabling.

- No special protocols.

- No special networking software.

- No special license.

- No special administrator or end-user training.

- Low-cost office / plant automation.

- Computer networking in historic buildings or cable-inaccessible areas.

- Mobile terminals and workstations

- Remote monitoring and access

- Energy management systems

- Remote Systems

Simply plug this device into your wall socket. Connect a PC, terminal or any other data device to the node and it's instantly connected.

This device uses a sophisticated technology that allows up to 7 bits of addressing which is 128 remote units to operate over the same power line system all with the same data integrity and reliability as a single two-node network. With the addition of a single modem and phone line you can link this device network to other LANs or WANs. Because it is not limited by line-of-sight restrictions, line infra-red, or broadcasting laws like radio frequency technology, power line networking is finding new applications all the time. Finally, anywhere you can run power, you can run our carrier current system.

Our other main concern is the safe use of our product, because our product uses the AC line as a medium, lethal voltages are present, which if not properly isolated within the circuit can cause serious damage not only to property but most important of to the life of the person using our product. We have used all the methods of safety isolation we know to make this circuit as safe and reliable to use as possible.

# Chapter 1

## **Introduction To Power Line Communication**

The term power line communications refers to a not quite so wireless form of wireless communications. Specifically, power line or "carriercurrent" systems employ existing ac power lines to transfer information which would normally require additional hard wire installation. Carrier current systems are attractive because they re-use existing electrical within a building. Typical applications include connections remote control (which we are doing here), security systems, and low speed data networking. Due to the fact that power lines encounter very large the main transformers, a phenomenon that tends inductances at to attenuate all but very low frequencies, they are limited to a region within a local area which uses the same mains transformer.

Using the AC line as a medium is a better alternative than using radio frequency transmitted over the air because first of all we are interested only in a small particular building, we also do not want to cause any RFI or interfere with any other government or private agencies that may be transmitting over the air using the same or a frequency near to ours. In Thailand it is also illegal to transmit any signal over the air without proper permission from the Post and Telegraph Authority of Thailand. Because of the abundance and availability of the Electric Line we choose to take advantage of it.

In order to send intelligence, or in other words our signal into the AC line we must use a carrier signal which will transport our information to its destination. We will use the most reliable method of modulation that we have learned in our classes which is suited to our particular case. From our experience and gained knowledge all fingers point at FSK. We will discuss this type of modulation and its details in further detail later in this project.

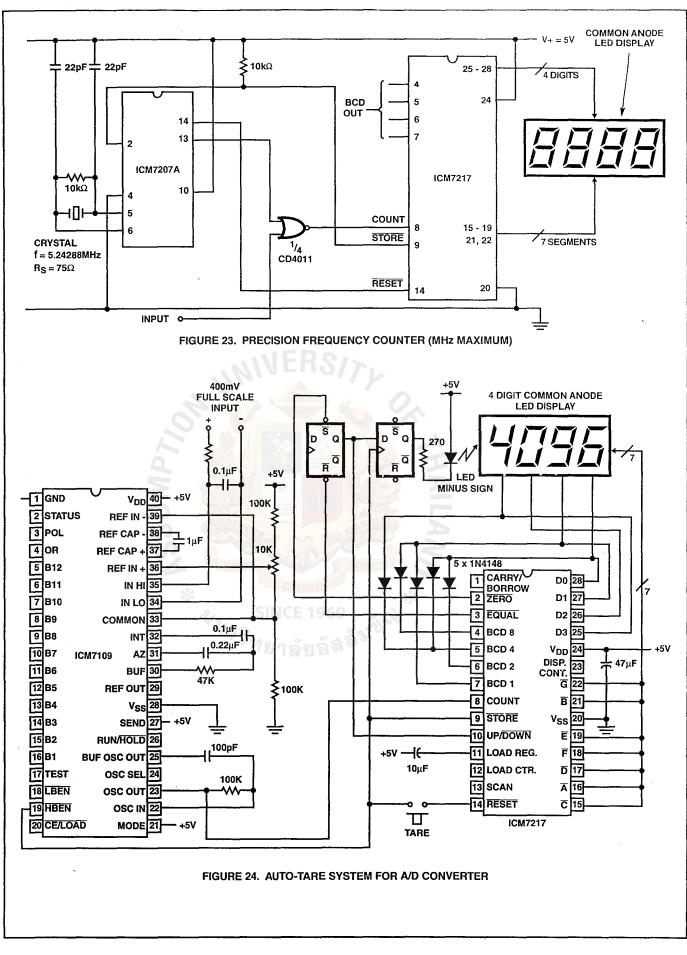

We are lucky that National Semiconductor company has developed a special IC dedicated to the transmission and reception of signals We are lucky that National Semiconductor company has developed a special IC dedicated to the transmission and reception of signals over the AC Electric line. UMC Semiconductors for their UM3750 Encoder/Decoder IC. Harris for their ICM7217CIPI real time clock Chip which very easily interfaced with the Atmel AT89C51 8-Bit Microcontroller of the MCS-51 family of Microcontrollers.

The Carrier Transmission System which we are going to use is not anything new. It has been used for many years in the electric industry. It is especially used when Electric Generating Plants communicate with each other. This means of communication is very reliable because it uses the high voltage AC transmission line instead of radio. This communication method also helps conserve Radio Spectrum Space. Another important factor is that through the utilization of this system of communication the electric power producing authorities can save a lot on communication costs.

The Carrier Current System does not generate RF which might cause interference with other communication systems. This method of transmission can be used for audio, data and even video type of modulation. The RF frequencies that it uses are in the range of 100 KHz till 500 KHz. Depending on the amount of accuracy or reproduction needed you can choose the type of modulation suited whether it be AM, FM or FSK to place information onto the carrier.

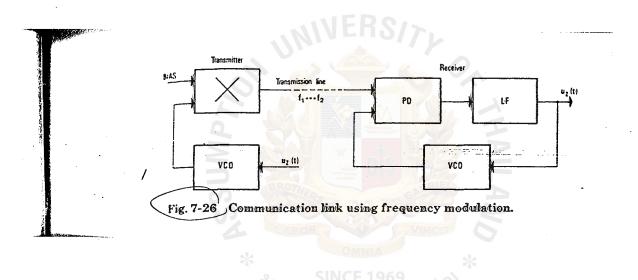

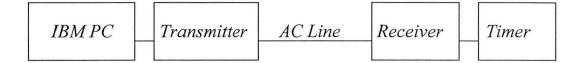

# **Short Description Of Project**

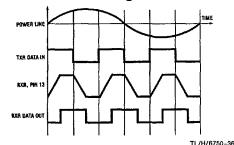

This circuit interfaces the IBM PC Parallel Port with a Microcontroller based timer through the AC Line. The circuit consists of two main blocks. The transmitter which is a little circuit connected to the PC Parallel port. The next main part of the project is the receiver which is at some remote location within the same building utilizing the same mains transformer and within the same phase. The medium of data transmission is the AC line.

# St. Gabriel's Library, Au

713 . . 1

### **Main Block Diagram**

### **Summary Of Various Parts Of The Block Diagram**

1. This is the master controller. It is a microcomputer which will be at the center of control located in the central office. The Microcomputer is programmed in High Level Language. In our project we used Microsoft Foxpro and Borland's Turbo Pascal as the main languages. The computer operator will be able to turn on 128 timers located in remote locations within the operator's local area.

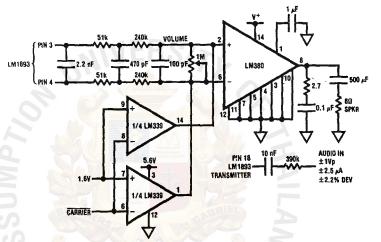

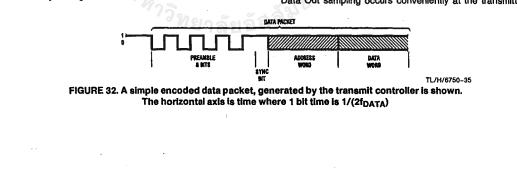

2. The transmitter is a circuit which comprises of the UM3750 encoder from UMC semiconductor company. This UMC chip will be instructed via the PC Parallel Port which of the 128 timers to turn on and for how long the timers should be turned on. The UMC chip will then send the data received from the PC Parallel Port which it has converted into serial form into the LM1893 Carrier Current Transceiver Chip. The LM1893 chip will then send this encoded data on to the AC line.

3. The AC line is the medium of data transfer.

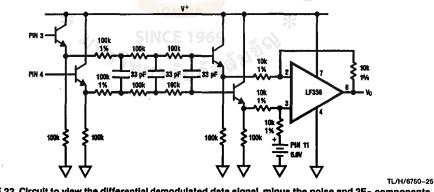

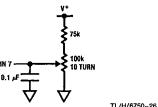

4. The Receiver comprises of the LM1893 Carrier Current Transceiver and the UM3750 decoder chip. The LM1893 will receive the encoded signals of the ac line and send them over to the UM3750 chip which will see if it is the one out of the 128 addresses being called. If the address received and the preset addresses match the UM3750 will send a signal to interrupt the microcontroller based timer.

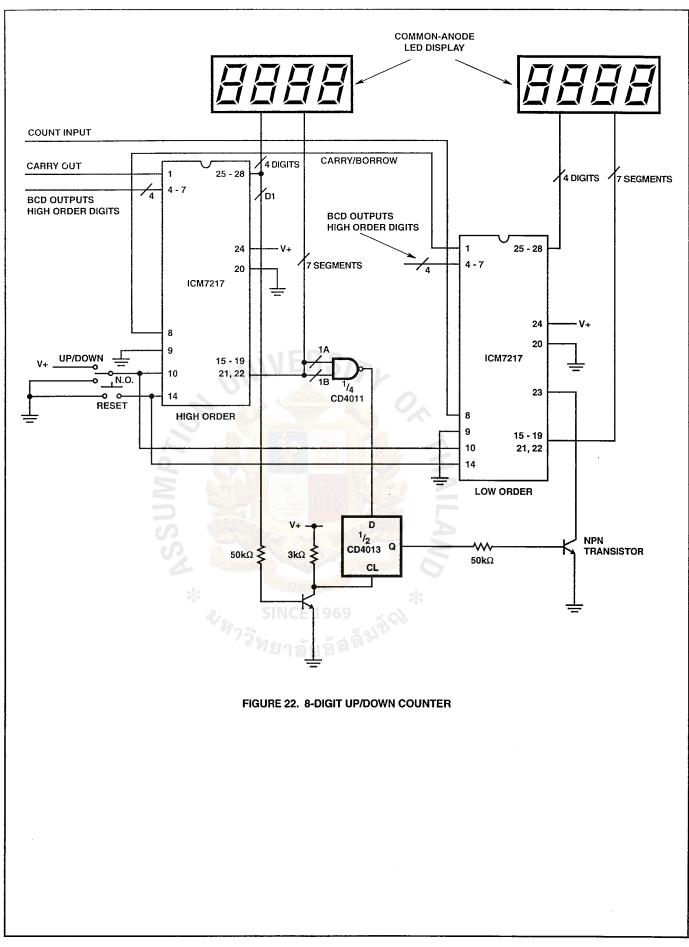

5. The microcontroller based timer will count the number of pulses sent by the receiver to determine how much time it should show on the display. The timer will then begin counting backwards from the time instructed by the receiver. This microcontroller will then turn on a relay which will switch on some other electrical device within that remote location.

#### **Existing Power Line Communications Standards**

There are four major power line communication standards in use today: X-10, CEBus, LONWorks, and Smart House. It is important to note that while all of these standards support power line communications, most of them also support other communications media, such as Infrared (IR) and Radio Frequency (RF). Some of these standards are summarized in the table below.

- X-10

- CEBus (EIA IS-60)

- LONWorks

- Smart House

- Developer

X-10 (USA-Corp.) Electronics Industry Association (EIA). Further developed by CEBusIndustry Council (CIC) Echelon Corp. Testing and certification programs led by LONMark Inter operability Assoc. Smart House Limited Partnership (Smart House LP) for the National Association of Home Builders.

Mentioning these protocols and company names are just here for theoretical purposes and to acknowledge that such products already exist prior to the making to this project. In no way did we copy or use any of these existing protocols in our project.

# Forecasted and Known Problems On Using This Carrier Current System

Since the transmitter operates in the 200-300 KHz range and is used to signals to a remote receiver via the AC power line. Either FM or AM modulation modes may be employed. FM is superior with regard to noise but AM modulation enables the use of simple low cost receivers. Effective

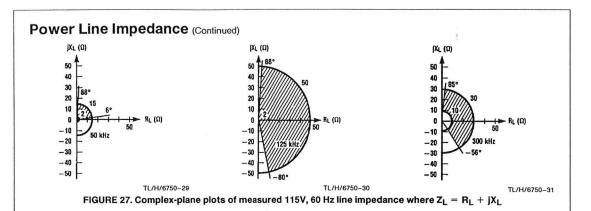

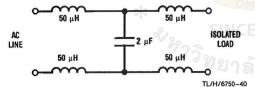

range depends mainly on the AC wiring and how it is connected in the building, the type of system employed (AM or FM) and the allowable signal to noise ratio, as well as the presence of any RF interference from sources such as motors, fluorescent lamps, triac and SCR operated devices (i.e. lamp dimmer switches), microprocessor devices, computer systems, and TV sets. The main culprit of line noise is the household television set which puts out a carrier of 15.7 Khz from the sweep circuits on to the ac line. All these devices can generate RF interference in the 200-300 KHz range. Another factor is the route the signal must take to the receiver, but most residential applications should experience no difficulty. In our project we use a low pass filter which we copied from a company that markets these readily available products to isolate the RF interference to our microcontroller based receiver.

Each factory, house or shop which might choose to use this product will have a different electrical lay out. This makes every electrical environment unique. We may not be able to expect the same results in two totally different electrical environments. Even the number and types of electrical devices connected up to the power line will be different in each situation providing us with another difficulty of varying impedance of the ac line. This varying impedance will make it difficult for us to have maximum power transfer at all times, since the impedance of the ac line is not constant. If we have many devices connected to the AC line at a present moment the impedance of the ac line may be very near short impedance.

Because of all this threat of noise on our ac line transmission medium we have agreed that we will use the FSK modulation method, which is much more reliable than other methods that we know of.

# Chapter 2

### **The PC Parallel Port**

We will attempt to describe interfacing to the IBM PC's parallel port in some detail here in this part of our report. The master controller is interfaced to the computer via its parallel port, so it is very essential that we define and understand properly the techniques of interfacing to the computer's parallel port. This information will be presented in a particular order in this report. First we will start with a description of the Standard Parallel Port (SPP), we will then advance on to hardware properties, giving the assigned port addresses. We will use the Parallel port to output 8 bits, which will also be covered. Before concluding we will list out how to use A Pascal Programming routine and a Foxpro program which will call upon the Pascal routine. I chose Foxpro because I am very familiar with it. The disadvantage of Foxpro is that it is not able to access the PC Parallel port. The Parallel Port is easily accessed in Pascal. Hence, I chose a combination of these two programming languages.

### **Introduction and Background of Parallel Ports**

The Parallel Port is the most used port for interfacing home made projects. The reason behind is that The Parallel Port can be much more readily and easily interfaced than the PC RS-232 Port (The Serial Port). Writing software to control the parallel port is also much easier that using the serial port.

The Parallel Port will allow the output of 8 bits at any one given time. The port is composed of 4 control lines, 5 status lines and 8 data lines. We will only use the Output from the Data Lines in this project. The Parallel Port is found commonly on the back of your PC as a D-Type 25 Pin female connector. There may also be a D-Type 25 pin male connector. This will be a serial RS-232 port and is a totally different port, one which we will not even touch in the fabrication of this project.

## Brief History On The Development Of The Parallel Port

Before 1994 there were no set standards as to how the Parallel Port should behave when connected to devices such as your humble printer, scanner, CD-ROM drive. Some may use TTL (Transistor to Transistor Logic) while others (more recent) may use CMOS (Complementary Metal Oxide Semiconductors) chips in their drivers.

The aim was to design new drivers and devices which were compatible with each other and also backwards compatible with the Standard Parallel Port (SPP). Compatibility, Nibble & Byte modes use just the standard hardware available on Parallel Port Cards while EPP & ECP modes require additional hardware which can run at faster speeds, while still being downwards compatible with the Standard Parallel Port.

Compatibility mode or "Centronics Mode" as it is commonly known, can only send data in the forward direction at a typical speed of 50 kbytes per second but can be as high as 150 kbytes a second. In order to receive data, you must change the mode to either Nibble or Byte Mode. Nibble Mode can input a nibble (4 bits) in the reverse direction. E.g. from device to computer. Byte mode uses the Parallel's bi-directional feature (found only on some cards) to input a byte (8 bits) of data in the reverse direction.

# **Hardware Properties**

Below is a table of the "Pin Outs" of the D-Type 25 Pin Connector. The D-Type 25 pin connector is the most common connector found on the Parallel Port of the computer, while the Centronics Connector is commonly found on Printers. The IEEE 1284 standard however specifies 3 different connectors for use with the Parallel Port. The first one, 1284 Type A is the D-Type 25 connector found on the back of most computers. The 2nd is the 1284 Type B which is the 36 pin Centronics Connector found on most printers.

IEEE 1284 Type C is also a 36 conductor connector, like the Centronics, but smaller. This connector is claimed to have a better clip

latch, better electrical properties and is easier to assemble. It also contains two more pins for signals which can be used to see whether the other device connected, has power. 1284 Type C connectors are recommended for new designs, so we can look forward on seeing these new connectors in the near future.

Pin No (D-Type 25) Pin No (Centronics) SPP Signal Direction In/out Register Hardware Inverted

1 Strobe In/Out Control 2 Data 0 Out Data 3 Data 1 Out Data 4 Data 2 Out Data 5 Data 3 Out Data 6 Data 4 Out Data 7 Data 5 Out Data 8 Data 6 Out Data 9 Data 7 Out Data 10 Ack In Status 11 Busy In Status 12 Paper-Out / Paper-End In Status **13 Select In Status** 14 Auto-Line feed In/Out Control 15 Error / Fault In Status 16 Initialize In/Out Control 17 Select-Printer / Select-In In/Out Control 18 Gnd

Table 1. Pin Assignments of the D-Type 25 pinParallel Port Connector.

The Printer/Parallel Port has three commonly used addresses. These are listed in a Table below. The 3BCh base address is not typically used today, but was once used when the Parallel Port was contained on the video card. The address locations for LPT1 & LPT2 are typically 378h & 278h respectively. The lower case h denotes that it is in hexadecimal. These addresses may change from machine to machine, depending on what value is set up in the machined CMOS. you can also

#### St. Gabriel's Library, Au

change the address of your PC parallel port in the CMOS setting area of your computer before you boot up the system.

#### **Address Notes:**

3BCh - 3BFh Used for Parallel Ports which were incorporated on to Video Cards - Does not support ECP addresses

378h - 37Fh Usual Address For LPT 1

278h - 27Fh Usual Address For LPT 2 Table 2 Port Addresses

When the computer is first turned on, the BIOS (Basic Input/Output System) will determine the number of ports you have and assign device labels LPT1, LPT2 & LPT3 to them. BIOS first looks at address 3BCh. If a Parallel Port is found here, it is assigned as LPT1, then it searches at location 378h. If a Parallel card is found there, it is assigned the next free device label. This would be LPT1 if a card wasn't found at 3BCh or LPT2 if a card was found at 3BCh. The last port of call, is 278h and follows the same procedure than the other two ports. Therefore it is possible to have a LPT2 which is at 378h and not at the expected address 278h.

The assigned devices LPT1, LPT2 & LPT3 should not be a worry to people wishing to interface devices to their PC's. Most of the time the base address is used to interface the port rather than LPT1. However, should you want to find the address of LPT1 or any of the Line Printer Devices, you can use a look up table provided by BIOS. When BIOS assigns addresses to your printer devices, it stores the address at specific locations in memory, so we can find them.

#### **Start Address Function**

0000:0408 LPT1's Base Address 0000:040A LPT2's Base Address 0000:040C LPT3's Base Address 0000:040E LPT4's Base Address (Note 1) Table 3 - LPT Addresses in the BIOS Data Area;

Note 1 : Address 0000:040E in the BIOS Data Area may be used as the Extended Bios Data Area in PS/2 and newer Bioses.

The base address usually called the Data Port or Data register, is simply used for outputting data on the Parallel Port's data lines (Pins 2-9). This port is normally a write only port. If you read from the port, you should get the last byte sent. However if your port is bi-directional, you can receive data on this address. We will not present any information on the Bi-directional Ports here in this project.

#### **Modulation & Demodulation**

Modulation is the process of superimposing a low frequency such as audio or data content onto a high frequency. Modulation is used at the transmitting end, where as demodulation is used at the receiving end. Modulation helps us transmit information many times farther than it could have travelled by itself. For example sound, in the frequency range of 20 Hz till 20 Khz, can only travel a limited distance. Electromagnetic waves on the other hand can be transmitted through space and can travel great distances. We use this property of the Electromagnetic wave to our advantage. We attach our information on to this Electromagnetic wave. This process of attaching information on to the Electromagnetic wave is called modulation. We then transmit this Electromagnetic wave, which is called carrier, through to space and a receiver tuned to the same exact frequency will pick up this Electromagnetic wave. The receiver then works to separate out this carrier from the information. The carrier is filtered out and has completed it's function and is no longer of use. We then can process and use the information that we have received. The process of separating this carrier wave from the information is opposite to the process of modulation, it is thus called demodulation. There are many methods of modulation available, we must however choose the cheapest and most suitable type of modulation to suit our particular need. We will not discuss modulation in greater detail because this subject is covered in many texts, any interested parties can refer to them.

#### **FSK Modulation Theory**

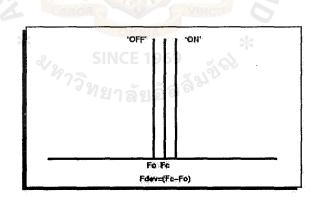

FSK modulation is a simplified form of FM. In true FM, an analog signal is represented by a linear frequency deviation from the center frequency. FSK is a binary form of FM that uses hard shifts between deviant frequencies to represent the data originally impressed on the carrier. The magnitude of frequency shift is directly related to the magnitude of the modulation source voltage.

The FSK modulation source is allowed two states: "on" and "off." When the modulation source is in an "off" state, the carrier frequency is shifted down from the center frequency. On the other hand, when the modulation source is in an "on" state, the carrier frequency is shifted up from the center frequency. The amount of carrier frequency shift is referred to as the frequency deviation.

In an FSK scheme, the amount of carrier frequency shift is referred to as the frequency deviation.

A carrier is always present with FSK modulation. This provides several benefits to the design engineer. First, the carrier will load the receiver at all times--providing greatly increased noise immunity. Secondly, the strength (or amplitude) of the carrier can be used to determine the quality of the incoming signal. A received strength signal indicator (RSSI) circuit is used to make this determination. This circuit outputs a voltage that corresponds to signal strength and has a typical dynamic range of 70 to 90 dB.

But there are drawbacks to having a continuous carrier. One drawback is power consumption. Since the carrier is continuously operating, it will require high supply current to operate.

FSK is a non-return to zero modulation method. As a result, the carrier should never be at the center frequency when modulation is present.

The benefit of a non-return to zero approach is noise immunity. Hysteresis can be applied to the detector, eliminating the effect of spurious frequency modulation generated from sources other than the data stream.

Since FSK relies on frequency change, and not amplitude change, to indicate data states, an FSK-based receiver is inherently immune to amplitude noise. This is of great importance in bands that are extremely crowded and feature a high potential for near-band interference, such as the Industrial, Scientific, and Medical (ISM) bands. This increased noise immunity suggests a potential for higher data rates. In fact, data rates up to 100 kb/s can be readily achieved with FSK-based systems.

Although FSK systems are immune to amplitude noise, they are very sensitive to frequency noise. Unwanted frequency changes caused by incircuit sources will ultimately lead to bit errors in the data stream.

As mentioned, simple hysteresis can be applied to the FSK detector to remove some of the frequency noise. But a stable frequency source must still be used to ensure good noise immunity. While SAW resonators work extremely well for low baud rate applications at lower frequencies, their inherent frequency inaccuracies make them poorly suited for FSK applications. Thus, a synthesized source based on a crystal reference must be used.

It is a well-known fact that crystals are superior to SAW resonators with regard to loaded Q and frequency accuracy. But crystals cannot be operated

in their fundamental mode at UHF. Instead, a crystal is used with a phase locked loop (PLL) to synthesize a high frequency. Although this technique is expensive and requires additional board space, it is the best method for attaining the tight frequency control necessary to achieve high data rates and noise immunity. It also provides the added benefit of channelization.

By using a divide-by-n PLL, the synthesized frequency can be set by changing the values of the internal counters. This allows an engineer to select a transmit or receive frequency from multiple channels. As a result, one transmitter or receiver can operate on many separate channels.

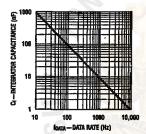

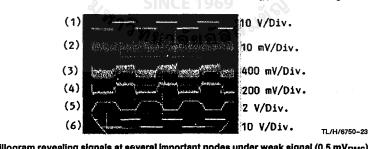

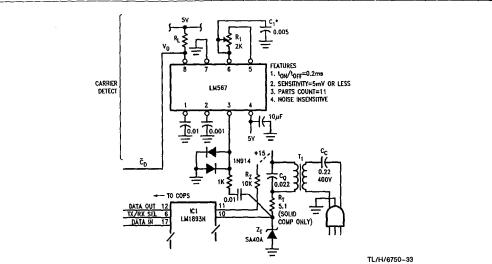

The LM1893 Chip From National Semiconductor is the only chip the I know of that can send FSK or FM modulated signals on to the AC line using just a single chip. During the designing of this circuit while I was deciding to which chips to use I came across the LM1893 chip in the Maplin Electronics Catalog. This chip is designed to transfer data over the mains between two remote locations on site on the same phase. The chip performs as a power line interface for half-duplex (bi-directional) in transmission mode a sinusoidal carrier is FSK in modulated and impressed on almost any power line via a rugged on chip driver. In reception mode a PLL-based demodulator and impulse noise filter combined to give maximum range. Data speeds up to 4800 baud are possible with carrier frequencies in the range of 50 to 300 Khz.

A full data sheet downloaded from http://www.national.com has been made available for reference and can be found at the end of this report in the appendix section.

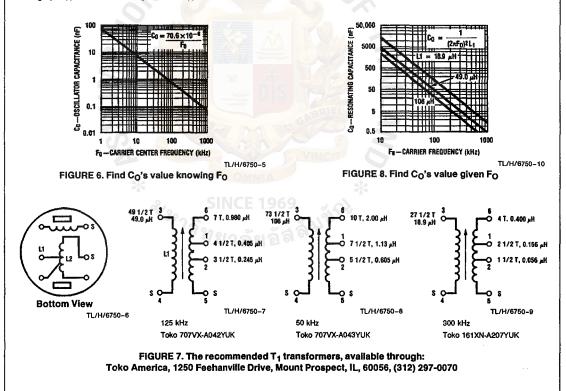

As for the design of the IF transformer was not necessary. We tried the commercially available IF BLACK 455 Khz transformer available from TOKO America.

In the Engineering Discipline as always, we will first start of with some calculations to determine the approximate value of the components which we will use during the experimental stage. The component values calculated will be different from the actual components we will use in our final design but they are necessary to establish some standard from where we can start experimenting.

#### Theory Of UM 3750 Decoder / Encoder Chip

The UM 3750 Decoder / Encoder chip is a chip with 12 address pins. Twelve pins gives 4096 addresses codes. Of the 12 pins we will use only 7 pins for addressing and 1 pin to trigger the UM 3750 chip to start transmitting. The reason for using this number of pins is that the PC parallel port can only output 8 data pins at one time. With a latch and other circuitry we could access all 12 address pins, by sending the data twice. In this circuit, however, for simplicity, lack of time and cost reduction sake we have chosen to use the 8 pins straight without any latching or any other fancy circuitry. The UM 3750 chip sends data serially on one line, this is exactly what we need to drive the LM1893 chip. It is also possible to design this same circuit without using this chip at all. Instead of using this chip we could have sent data from the PC serial port and at the decoding end we could have used a microcontroller to decode the serial data. Us being us, lazy and always looking for an easy way out chose this chip. The PC serial port involves a lot of interfacing experience and programming expertise to use. The Parallel port can be accessed in Pascal with using a 5 line source code program. Something that is an excuse for a data sheet can be found at the end of this project in the appendix section.

### Theory of Microcontroller Timer and Display

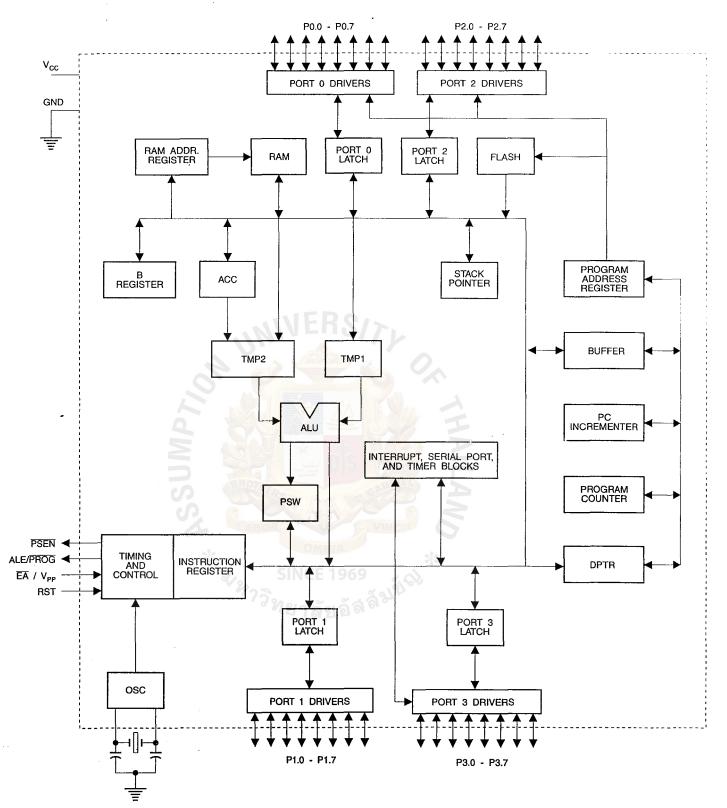

You may ask why we choose to include and design our project around Microcontrollers. Well gone are the days when a complex project required a bag full of TTL chips, bread boards and millions of wires. The thing is that Hardware is expensive and software is cheap (only if you write it your self). Our project can then be easily modified by software without the need for extra hardware or soldering. Here we will use the AT89C51 a Microcontroller from the famous Intel family of chip which is microprocessors and microcontrollers. Here we will attempt to describe this MSC-51 family in some detail. The 8051 chip is also known as an embedded microcontroller. It is important that you first understand the difference between the word microprocessor and microcontroller. The microprocessor is the part of a computer without memory, I/O, and peripherals needed for a complete system. For example, 8088 and 80286 chips are microprocessors. All the other chips in the IBM PC add to the features not found in the microprocessor itself. The hardware designer can choose to implement from those features in different ways, although the designer has a choice of design at the end of the day it is still an IBM PC clone.

a microprocessor is combined with When I/O and memory peripherals functions, the combination is called a microcomputer The fact that combining the CPU with memory and I/O products produces a microcomputer also holds true at the chip level. Generally speaking, microcomputer chips are designed for very small computer-based products that don't need all the functions of a full computer system. In control applications, even a few chips that are needed to cost-sensitive support a CPU like 8088 or Z80 are too many. Instead designers employ a single chip microcomputer to handle specific control activities. When single chip microcomputers are designed to be used in industrial control systems they are called microcontrollers. Basically there are no difference between microcomputers and microcontrollers, the name depends on how we use them.

Frequently microcontrollers are used to replace circuit functions that often require too many low-level chips. The IBM PC keyboard is a prime example of the use of a microcontroller chip.

The Intel 8051 chip is a classic microcontroller (it is a generation more advanced than the 8742) is a true single chip microcomputer containing parallel I/O, counters and timers, serial I/O, RAM and Flash Eprom. There are many different versions of this microcontroller but we chose to use the ATMEL 8051 Flash Microcontroller because of it's cheap price, wide availability, easy programming and easy re-programming. The 8051 contains 4K bytes of RAM which will hold the program and it's system variables.

Using the 8051 chip is as simple as hooking up the power supply and a clock crystal. We also must remember that a single chip microcontroller replaces all the digital logic you would normally used for control, timing and so forth. You need only to add the keyboard, displays, switches, relays and other specific I/O that actually makes up the final product.

A single I/O port can scan a 16 key matrix. With an additional output bit it can drive a 2-line by 20 character smart liquid display at the same time. The remaining I/O bits can handle triacs of power FETS for AC or DC control. Burn a program into the microcontroller's flash and you have a real time power controller. Run the serial port through a MAX121 RS-232C level converter, and you have a standard serial port for remote control or status monitoring at your master computer.

If you don't need the serial port, counters, timers, and external interrupts the 8051 can use those bits as another I/O port. The point of this is that the "computer" part of your system need not require elaborate hardware. For a unit of reasonable size you will spend most of your time on the I/O devices rather than the 8051 circuit.

The main benefit of using a microcontroller is the ease in adding new features to your system, just by changing the program, not changing the circuit board connections you can give your system a completely new personality. Try doing that with a board full of TTL control logic!

Now to come to the software part. If you have ever written or are familiar with assembly language programming for any microprocessor you will find that the 8051 will have many same instructions. There is however a big difference in internal and external memory addressing. In this project we will only use internal memory addressing so this will be discussed no further.

To go into greater detail of the internal memory of the microcontroller we will explain the four types of addressing here. There are four addressing modes direct, intermediate register, and register indirect. Direct mode embeds an internal an address in the instruction. Immediate mode uses the data value itself. Register and register indirect use a register number, with indirect addressing taking the contents of that register as a direct address to access the data.

The 8051 has a single accumulator called ACC or A depending on the use of the instruction. Nearly all instructions use the accumulator in one way or another.

Because the microcontroller applications require handling at least few I/O bits, the 8051 has a rich selection of bit manipulation instructions that are completely separate from standard byte instructions. A single instruction set can set, clear, compliment or copy any bit in internal data memory. The on chip I/O ports show up in that address space, so there is no need for the "read, mask, set, combine, write" instructions found in most other microprocessors.

Unlike the intel 8088 or Z80 microprocessor families, the 8051 has no explicit I/O instructions. The on chip I/O ports are mapped into the internal data memory-address space and accessed with the same MOV instruction used for other transfers.

There is however an ugly side of microcontrollers is that of getting the software to work. But thanks to the special debugger I borrowed off my friend I can debug programs on my PC and immediately upload them into the debugger and test my program out. I can keep doing that until my program works perfectly. Also using a logic probe and an oscilloscope helps a lot. With this debugger you can use program breakpoints to stop execution at specific 8051 instructions or when a given condition

#### St. Gabriel's Library, Au

occurs. Also, since the debugger records each particular variable you can examine the contents of the variable.

Ι After debugging the program programmed the embedded microcontroller with a ACP programmer which was available for use in The Network Research Center 4th Floor **E-Building** Assumption programmer is a handy one because University. This it can be programmed by a PC or programmed directly into it's keyboard. The programmer was purchased in Ban Moh in China Town from a shop called Electronics Source LTD. The price of this programmer was approximately 8,000 Bahts, that was before the US dollar sky rocketed to 50 Bahts.

A detailed data sheet of the Microcontroller from Atmel Electronics which is used in this project can be found at the appendix at the end of this project.

## **Timer Circuit Description**

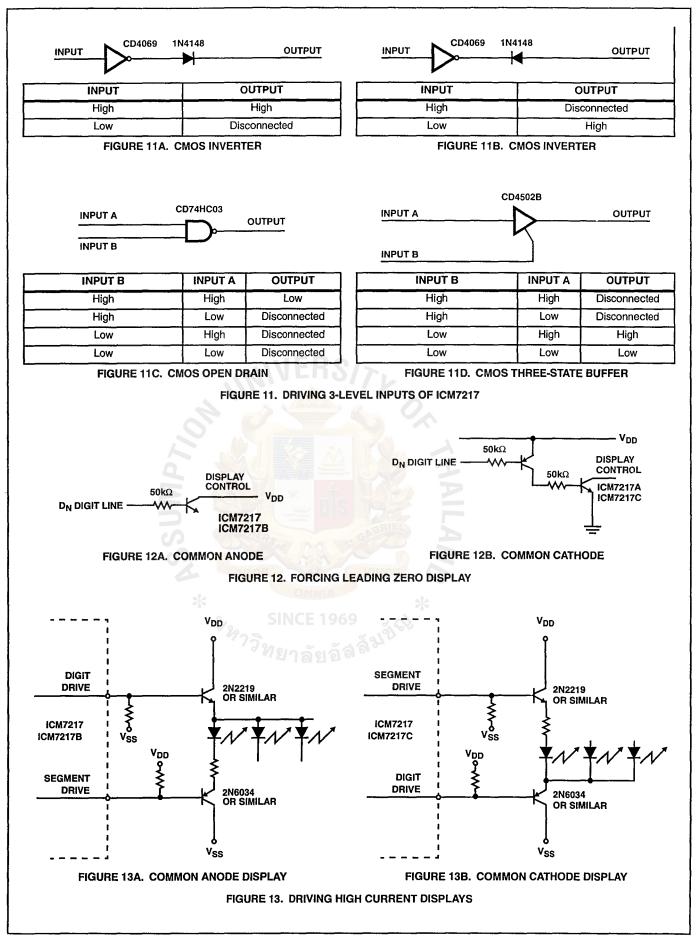

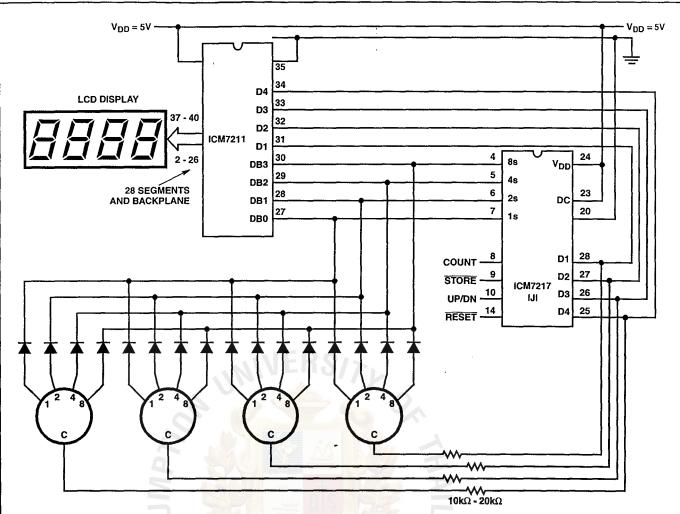

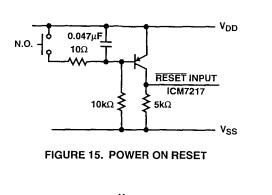

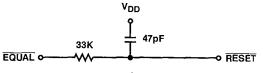

Now it is time to explain how the timer circuit we designed works. This is a behind the scenes view of what happens after the microcontroller in interrupted. Before getting into the details of the program we will first discuss the working of the ICM7217CIPI counter chip.

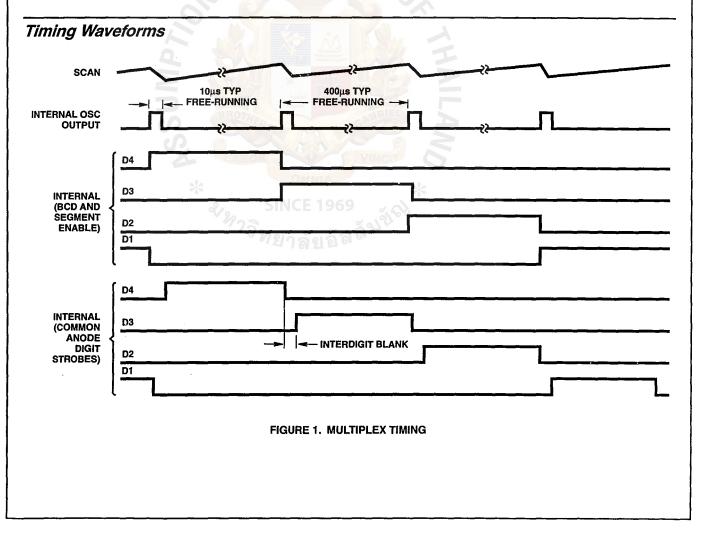

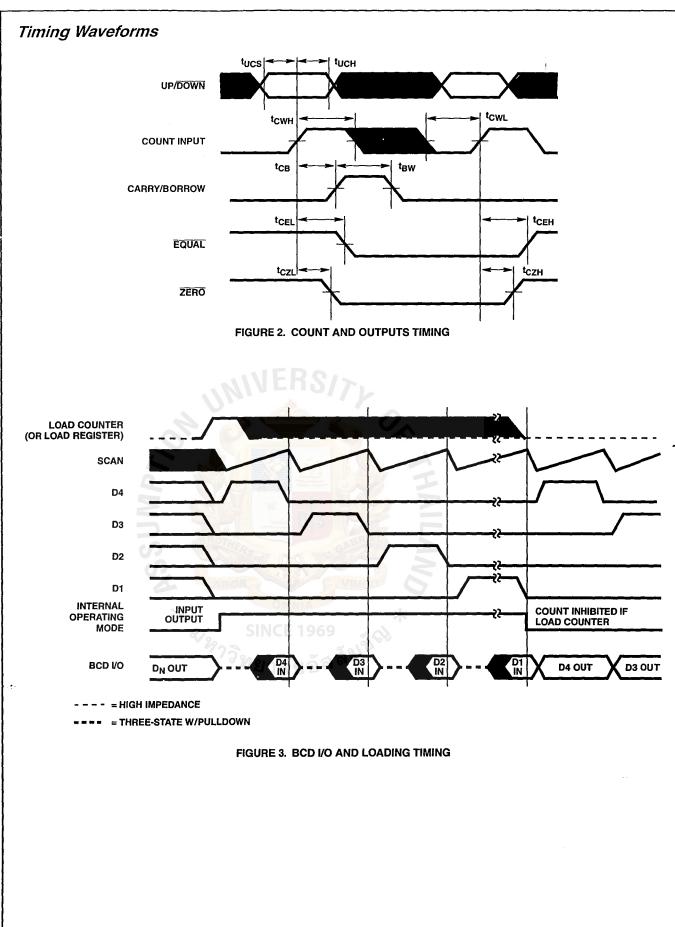

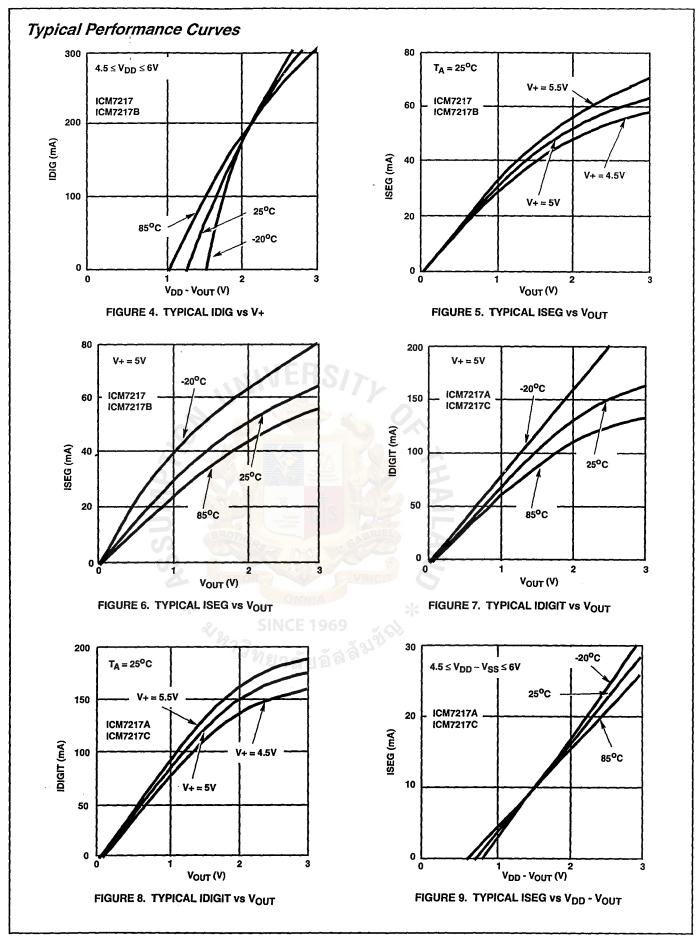

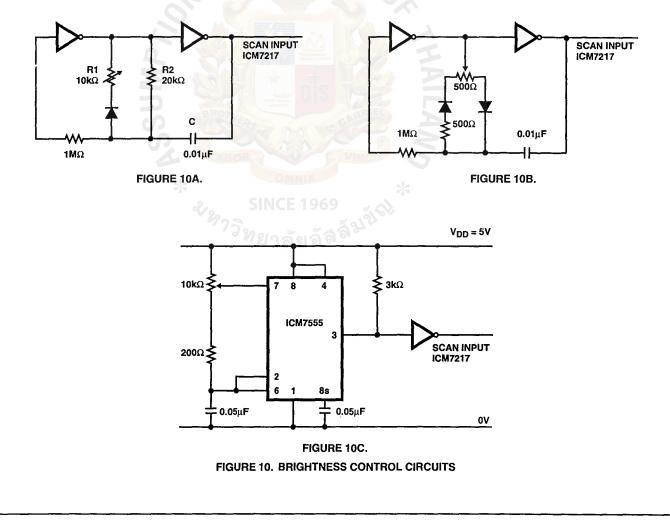

Without the ICM7217CIPI chip from Harris Semiconductors, driving and multiplexing 4 seven segment displays is no easy job. Thanks to Harris, this counter chip is very easily interfaced to our microcontroller. The chip has a special ZERO output pin which is active low. This pin will go low if the number that is displayed on the seven segment display is zero. There is a count up/down mode pin which if high sets the chip into count up mode and if low will set the chip into count down mode. If we send pulses to the count pin the counter will count up or down one pulse depending whether the mode pin has been set to count up or down. This chip will multiplex 4 seven segment displays by itself with no additional circuitry. Basically all our microcontroller is doing in this circuit is providing the right information in pulses, count mode and resetting the ICM7217CIPI chip.

Now I will describe in plain English what the assembly program that is contained in the microcintroller is doing. Our microcontroller works at very high speed, in this circuit the crystal clock frequency is 11.0592 Mhz. The first section of the program there is a delay, this delay is there so that the ICM7217CIPI can get up on its feet and get ready to run. The program then sends a pulse which goes from high to low and goes back to high to reset the ICM7217CIPI. This pulse is sent out of pin 4 of the microcontroller to pin 14 of the ICM7217CIPI chip. We then disable all external interrupts just in case any were set up in the starting up of the chip We then proceed to clear the values in various addresses before we set the timer mode. We then define the hardware interrupt procedure. This procedure first will debounce the interrupt that is provide a small delay. We then start off the timer so that it will provide a software interrupt every one minute. After that the microcontroller is instructed to read the input of the dip switch to see how many pulses it should send to the count pin. The microcontroller then sends via pin its pin 2 to pin 10 of ICM7217CIPI to send it to count up mode. It then sends a pulse train via its pin 1 to pin 8 of ICM7217CIPI to tell it to count up to the value set on the dip switch. Every one minute the software interrupt is serviced, here it will first check pin 21 of microcontroller if it is not low the microcontroller will set the ICM7217CIPI into count down mode and will send one pulse to make the ICM7217CIPI count down. If the input on pin 21 is low the program will reset the ICM7217CIPI and will cut the power from the relay.

# **Chapter 3**

# Schematic Diagrams in this Chapter

- Schematic Diagram Microcontroller Based Timer

- Schematic Diagram Receiver

- Schematic Diagram Transmitter

MICROCONTROLLER TIMER SCHEMATIC DIAGRAM

#### SCHEMATIC OF LM1893 AC LINE RX WITH UM3750 DECODER

St. Gabriel's Library, Au

#### SCHEMATIC OF LM1893 AC LINE TX WITH UM3750 ENCODER

# Chapter 4

### **Pascal & The PC Parallel Port**

This program will output the decimal value of 85 on to the Parallel Port for one second then output the value on the Parallel Port to the decimal value 0.

> Program Parallel(input, output); Uses Dos,Crt; Begin PORT[\$378]:=85; DELAY(1000); PORT[\$378]:=0; end.

### Foxpro Program Source Code

\*: Procedure file: C:\FOXPRO\ACLINE\MAIN.PRG \*. \*. System: Data Communication On Electric Line \*. Author: Cherdchai J(361-6310) Suvir K(361-6898) Copyright (c) 1998, ABAC EN 4902 Engineering Project II \*. \*: Last modified: 03/15/98 15:06 \*: \*: Procs & Fncts: EXIT \*: \*: Calls: SET SETS (procedure in SET SETS.PRG) (procedure in MAIN.PRG) \*. : EXIT : DEV1.PRG \*: \*: : BIGLETT() (function in BIGLETT.PRG) \*: : UNTALK() (function in UNTALK.PRG) \*.

\*: Documented 03/15/98 at 17:22 FoxDoc version 2.10f

inmain=.T.

DO set\_sets

SET ESCAPE OFF

SET SYSMENU TO

ON ESCAPE SET SYSMENU TO DEFA

SET SYSMENU AUTOMATIC

PUBLIC m.company

m.company= " Data Transmission On AC Line Project "

m.company1=" Electronics & Engineering Project II "

m.company2=" Cherdchai Jungsatitkul 361-6310 "

m.company3=" Suvir Kumar 361-6898 "

DEFINE PAD \_qoi11lm10 OF \_msysmenu PROMPT "Turn On Device" COLOR SCHEME 3

DEFINE PAD \_qoi111mbx OF \_msysmenu PROMPT "E\<xit Program " COLOR SCHEME 3

ON PAD \_qoi111m10 OF \_msysmenu ACTIVATE POPUP employee ON SELECTION PAD \_qoi111mbx OF \_msysmenu DO EXIT

DEFINE POPUP employee MARGIN RELATIVE SHADOW COLOR SCHEME 4

DEFINE BAR 1 OF employee PROMPT "Device \<One" DEFINE BAR 2 OF employee PROMPT "Device \<Two " DEFINE BAR 3 OF employee PROMPT "Device T\<hree" DEFINE BAR 4 OF employee PROMPT "Device \<Four" DEFINE BAR 5 OF employee PROMPT "Device F\<ive"

ายาลัยอิลโ

ON SELECTION BAR 1 OF employee DO dev1

\*\*\*MAIN\_PROGRAM\*\*\* ON SELECTION MENU\_msysmenu CLEAR WINDOWS ALL CLEAR =biglett(02,1,'DATA TX') =biglett(11,1,'AC LINE')

```

@ 18,00 SAY

@ 19,00 SAY '3

31

@ 20,00 SAY '3

31

31

@ 21,00 SAY '3

31

@ 22,00 SAY '3

@ 23,00 SAY

(a) 19,(40-(LEN(ALLTRIM(m.company))/2)) SAY ALLTRIM(m.company)

@ 20,(40-(LEN(ALLTRIM(m.company1))/2)) SAY

ALLTRIM(m.company1)

@ 21,(40-(LEN(ALLTRIM(m.company2))/2)) SAY

ALLTRIM(m.company2)

@ 22,(40-(LEN(ALLTRIM(m.company3))/2)) SAY

ALLTRIM(m.company3)

DO WHILE inmain

USE

=untalk()

CLEAR WINDOWS

SET SAFETY OFF

ACTIVATE MENU msysmenu

ENDDO

******

*1

*!

Procedure: EXIT

*!

*!

Called by: MAIN.PRG

*1

PROCEDURE EXIT

FOR i = 1000 TO 1500 STEP 200

SET BELL TO i,1

?? CHR(7)

ENDFOR

inmain=.F.

SET SYSMENU TO DEFA

```

CLEAR WINDOWS ALL RELEASE ALL \*quit RETURN \*: EOF: MAIN.PRG

```

*.

*: Procedure file: C:\FOXPRO\ACLINE\SET SETS.PRG

* .

*:

System: Data Communication On Electric Line

Author: Cherdchai J(361-6310) Suvir K(361-6898)

*.

Copyright (c) 1998, ABAC EN 4902 Engineering Project II

*.

*: Last modified: 05/20/94 9:43

*:

*: Procs & Fncts: SET SETS

*.

*.

Documented 03/15/98 at 17:22

FoxDoc version 2.10f

*1

*1

Procedure: SET SETS

*1

*1

Called by: MAIN.PRG

*1

* | * * * * * * * * * * * * * *

PROCEDURE set sets

*****

*****

DO set sets

*

Version # 1.0 FP

Date: 02-05-90

* Programmed by: Malcolm C. Rubel

*

* Copyright (c) 1990

* Performance Dynamics Associates

All Rights Reserved

*

¥

```

#### St. Gabriel's Library, Au

\* Note: SET SETS sets all sets to the setting to which

\* they should be set when you set out to set up your

\* application. Set it in your mind that some of the sets

\* are not set to the standard setting for sets.

SET ALTERNATE OFF SET ALTERNATE TO \*SET AUTOSAVE on SET BELL TO 440,2 SET BELL OFF SET BLINK OFF SET BLOCKSIZE TO 64 SET BORDER TO SET BRSTATUS OFF SET CARRY OFF SET CENTURY OFF SET CLEAR ON SET CLOCK OFF SET COMPATIBLE OFF SET CONFIRM OFF SET CONSOLE ON SET CURRENCY TO SET CURRENCY LEFT SET CURSOR ON SET DATE BRITISH \*SET DEBUG off **SET DECIMALS TO 2** SET DELETED ON SET DELIMITERS TO '[]' SET DELIMITERS OFF SET DEVELOPMENT ON SET DEVICE TO SCREEN SET DOHISTORY OFF SET ECHO OFF SET ESCAPE OFF SET EXACT ON SET EXCLUSIVE OFF SET FIELDS TO SET FIELDS OFF

&& not the normal tone

&& single line border

&& dollar default

&& British default

CE 1969

&& not the default && but do not use it && Crazy About You OUI

| SET FIXED ON<br>SET FORMAT TO<br>SET FULLPATH ON                                                                                                                                                                                    | && not a default                         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

| SET FUNCTION 1 TO *<br>SET FUNCTION 2 TO *<br>SET FUNCTION 3 TO *<br>SET FUNCTION 4 TO *<br>SET FUNCTION 5 TO *<br>SET FUNCTION 6 TO *<br>SET FUNCTION 7 TO *<br>SET FUNCTION 8 TO *<br>SET FUNCTION 9 TO *<br>SET FUNCTION 10 TO * | && clears function key<br>&& assignments |

| IF FKMAX() = 12<br>SET FUNCTION 11 TO *<br>SET FUNCTION 12 TO *                                                                                                                                                                     | && twelve function keys                  |

| ENDIF                                                                                                                                                                                                                               |                                          |

| SET HEADING OFF<br>SET HELP ON<br>SET HISTORY OFF<br>SET HOURS TO 12<br>SET INTENSITY ON<br>SET LOGERRORS OFF<br>SET MARGIN TO 10<br>SET MARK TO '/'<br>SET MEMOWIDTH TO 50<br>SET MESSAGE TO 24                                    | && not a default<br>&& not a default     |

| SET MUSSAGE TO 24<br>SET MOUSE TO 5<br>SET MOUSE ON<br>SET NEAR ON<br>SET NOTIFY ON<br>SET ODOMETER TO 100<br>SET POINT TO '.'<br>SET PRINTER OFF<br>SET SAFETY OFF<br>SET SCOREBOARD OFF                                           | && not a default                         |

SET SEPARATOR TO ',' SET SHADOWS ON SET SPACE ON SET STATUS OFF \*SET STEP off SET STICKY ON SET SYSMENU OFF SET TALK OFF SET TALK OFF SET TOPIC TO SET TYPEAHEAD TO 20

```

IF VERSION() > 'FoxPro 1.01')

```

SET UDFPARMS TO VALUE && version 1.02 command ENDIF

SET UNIQUE OFF

= INSMODE(.T.)

= CAPSLOCK(.F.)

= NUMLOCK(.T.)

#### RETURN

\*: EOF: SET SETS.PRG \*\*\*\*\*\*\*\* \*. \*: Program: C:\FOXPRO\ACLINE\DEV1.PRG \*• \*: System: Data Communication On Electric Line Author: Cherdchai J(361-6310) Suvir K(361-6898) \*: Copyright (c) 1998, ABAC EN 4902 Engineering Project II \*: \*: Last modified: 03/15/98 15:36 \*: \*: Called by: MAIN.PRG \*: \*. Calls: WEXPLODE() (function in WEXPLODE.PRG) \*: : BIGLETT() (function in BIGLETT.PRG) \*. : YESNO() (function in YESNO.PRG) : WIMPLODE() \*: (function in WIMPLODE.PRG)

```

*:

*•

Documented 03/15/98 at 17:22

FoxDoc version 2.10f

=wexplode('abac',1,0,24,79,'Turn On Device One')

=biglett(3,0,'Device')

=biglett(13,0,'One')

choice=yesno('Turn On Device One')

IF choice=.T.

! device1.exe

ENDIF

=wimplode('abac','Turn On Device One')

RETURN

*: EOF: DEV1.PRG

*.

*: Procedure file: C:\FOXPRO\ACLINE\WEXPLODE.PRG

*:

*.

System: Data Communication On Electric Line

*.

Author: Cherdchai J(361-6310) Suvir K(361-6898)

*.

Copyright (c) 1998, ABAC EN 4902 Engineering Project II

*: Last modified: 03/21/94

20:43

*.

*: Procs & Fncts: WEXPLODE()

*.

*.

Documented 03/15/98 at 17:22

FoxDoc version 2.10f

*1

*!

Function: WEXPLODE()

*1

*!

Called by: DEV1.PRG

*!

*!

Calls: POPERROR()

(function in POPERROR.PRG)

*1

FUNCTION wexplode

PARAMETERS w name, ul rr, ul cc, lr rr, lr cc, b type;

b title, c scheme

PRIVATE w name, ul rr, ul cc, lr rr, lr cc, b type, ;

```

b type, c scheme PRIVATE mid rr, mid cc, rr it, cc it, max it, b start PRIVATE rr incr, cc incr, i, b incr, pcount, rvalue \*\*\*\*\*\*\*\*\*\* wexplode(<expC1>,<expN1>,<expN2>,<expN3>,<expN4>; \* [,<expC2>][,<expC3>[,<expN5>]]) \* Version # 2.1 Date: 08-29-91 \* Programmed by: Malcolm C. Rubel Copyright (c) 1990,91 Performance Dynamics Associates \* All Rights Reserved \* Note: Function takes window name, window coordinates, \* and optionally the window type and explodes the window \* up to that size. Function returns the name of the \* window that was active before the window exploded on \* screen. If no window was active, the function returns \* a null value. \* Modified 10-1-90 to include a color scheme choice. \* Modified 1-23-91 to reduce the use of macro expansion \* to a minimum. \* Modified 8-29-91 to change WONTOP to WOUTPUT. \*\*\*\*\*\* pcount = PARAMETERS() & how many were passed rvalue = WOUTPUT() && active window && not enough parameters IF pcount < 5= poperror('Not enough parameters passed to WEXPLODE. '+; 'Window will not pop.') **RETURN**(rvalue) ENDIF IF pcount = 5b type = " c scheme = 1**ENDIF**

```

IF pcount = 6

IF TYPE('b_type') = 'C'

IF LEN(b_type) = 1

b_type = UPPER(b_type)

b_title = "

c scheme = 1

ELSE

b_title = b_type

b type = "

c scheme = 1

ENDIF

ELSE

IF TYPE('b type') = 'N'

b_type = "

b_title = "

c_scheme = b_type

ENDIF

ENDIF

ENDIF

IF pcount = 7

IF TYPE('b title') = 'N'

c_scheme = b_title

b. title = "

ENDIF

ENDIF

b_type = UPPER(b_type)

DO CASE

```

42

CASE b\_type = 'D' b\_type = 'DOUBLE'

CASE b\_type = 'P' b\_type = 'PANEL'

OTHERWISE b type = "

ENDCASE

\*\*\* first find the screen coordinates for the middle of the \*\*\* box for both row and column

$mid_rr = ul_rr + INT((lr_rr - ul_rr)/2)$  $mid_cc = ul_cc + INT((lr_cc - ul_cc)/2)$

\*\*\* how many 'steps' will we have to take in both the x

\*\*\* and y axes to 'grow' the box to its full size

$rr_it = INT((lr_rr - ul_rr)/2)$ cc\_it = INT((lr\_cc - ul\_cc)/2)

\*\*\* if the box is greater than the minimum size that makes\*\*\* exploding worthwhile

IF rr\_it  $\geq 4$  .AND. cc\_it  $\geq 4$

\*\*\* which is larger the x or y axis. use the larger axis \*\*\* to control the explosion.

\*\*\* explode the window in steps

FOR i = b\_start TO max\_it - 2 STEP b\_incr

## St. Gabriel's Library, Au

rr\_incr = INT(rr\_it\*(i/max\_it))

cc\_incr = INT(cc\_it\*(i/max\_it))

DEFINE WINDOW (w\_name); FROM mid\_rr-rr\_incr,mid\_cc-cc\_incr; TO mid\_rr+rr\_incr, mid\_cc + cc\_incr; &b\_type COLOR SCHEME c\_scheme ACTIVATE WINDOW (w\_name)

= INKEY(.01)

&& pause just a bit

ENDFOR

ENDIF

\*\*\* now activate the real window!

b title = IIF(EMPTY(b title),", 'TITLE "' + b title + '"')

```

DEFINE WINDOW (w_name) FROM ul_rr, ul_cc TO lr_rr,lr_cc ;

&b_type &b_title COLOR SCHEME c_scheme

ACTIVATE WINDOW (w_name)

```

```

RETURN(rvalue)

```

\*: EOF: WEXPLODE.PRG

```

*.

*: Procedure file: C:\FOXPRO\ACLINE\WIMPLODE.PRG

*.

*.

System: Data Communictaion On Electric Line

*.

Author: Cherdchai J(361-6310) Suvir K(361-6898)

*.

Copyright (c) 1998, ABAC EN 4902 Engineering Project II

*: Last modified: 09/12/91

0:00

*:

*: Procs & Fncts: WIMPLODE()

*.

*:

Documented 03/15/98 at 17:22

FoxDoc version 2.10f

```

```

*! Function: WIMPLODE()

```

\*!

\*!

```

*! Called by: DEV1.PRG

```

\*!

FUNCTION wimplode

PARAMETERS w\_name, b\_type, c\_scheme PRIVATE w\_name, b\_type, c\_scheme PRIVATE mid\_rr, mid\_cc, rr\_it, cc\_it, max\_it, b\_fin, rr\_incr PRIVATE cc\_incr, b\_incr, lr\_rr, lr\_cc, ul\_rr, ul\_cc, pcount PRIVATE i, rvalue

```

******

```

```

* wimplode(<expC1>[,<expC2>][,<expN>])

```

- \* Version # 2.1 Date: 08-29-91

- \* Programmed by: Malcolm C. Rubel

- \*

\*

- \* Copyright (c) 1990,91

- \* Performance Dynamics Associates

- \* All Rights Reserved

- \* Note: Function takes window name, and optionally, the

- \* window type, and implodes the window. Function returns

- \* the name of the window that was active when the

- \* function was called.

- \* Modified 10-1-90 to include a color scheme choice.

- \* Modified 1-23-91 to reduce the use of macro expansion

- \* to a minimum.

```

* Modified 8-29-91 to change WONTOP to WOUTPUT.

```

\*\*\*\*\*\*\*

```

pcount = PARAMETERS()

rvalue = WOUTPUT()

```

&& how many were passed && active window

```

IF pcount = 1

b_type = "

c_scheme = 1

ENDIF

```

```

IF pcount = 2

IF TYPE('b_type') = 'C'

b type = UPPER(b_type)

c scheme = 1

ELSE

IF TYPE('b type') = 'N'

b type = "

c_scheme = b_type

ENDIF

ENDIF

ENDIF

DO CASE

CASE b type = 'D'

b_type = 'DOUBLE'

CASE b type = 'P'

b_type = 'PANEL'

OTHERWISE

b_type = "

```

**ENDCASE**

\*\*\* find out if the named window is the active window. If \*\*\* it is not, activate it before imploding it.

IF WONTOP() # UPPER(w\_name) ACTIVATE WINDOW (w\_name) ENDIF

\*\*\* get the row and column coordinates for the window.

ul\_rr = WLROW() ul\_cc = WLCOL() lr\_rr = ul\_rr + WROWS() lr\_cc = ul\_cc + WCOLS() && upper left hand corner

&& upper left hand corner

&& lower right corner

&& lower right corner

\*\*\* first find the screen coordinates for the middle of the \*\*\* box for both row and column

$mid_rr = ul_rr + INT((lr_rr - ul_rr)/2)$  $mid_cc = ul_cc + INT((lr_cc - ul_cc)/2)$

\*\*\* how many 'steps' will we have to take in both the x \*\*\* and y axes to implode the box

$rr_it = INT((lr_rr - ul_rr)/2)$ cc\_it = INT((lr\_cc - ul\_cc)/2)

\*\*\* if the box is greater than the minimum size that makes \*\*\* imploding worthwhile

IF rr\_it  $\geq 4$  .AND. cc\_it  $\geq 4$

\*\*\* which is larger the x or y axis. use the larger axis \*\*\* to control the implosion.

\*\*\* implode the window in steps

FOR i = max\_it - 2 TO b\_fin STEP b\_incr

rr\_incr = INT(rr\_it\*(i/max\_it))

cc\_incr = INT(cc\_it\*(i/max\_it))

DEFINE WINDOW (w\_name) FROM mid\_rr-rr\_incr,mid\_cc-cc\_incr; TO mid\_rr+rr\_incr, mid\_cc + cc\_incr; &b\_type COLOR SCHEME c\_scheme ACTIVATE WINDOW (w\_name)

```

= INKEY(.01)

```

&& pause just a bit

ENDFOR

**ENDIF**

\*\*\* now activate the real window!

RELEASE WINDOW (w\_name)

```

RETURN(rvalue)

*: EOF: WIMPLODE.PRG

*.

*: Procedure file: C:\FOXPRO\ACLINE\YESNO.PRG

*.

*.

System: Data Communication On Electric Line

Author: Cherdchai J(361-6310) Suvir K(361-6898)

*.

Copyright (c) 1998, ABAC EN 4902 Engineering Project II

*.

*: Last modified: 09/12/91 0:00

*.

*: Procs & Fncts: YESNO()

*.

*.

Documented 03/15/98 at 17:22

FoxDoc version 2.10f

*1

ทยาลัยอัลลิ

*!

Function: YESNO()

*!

*!

Called by: DEV1.PRG

*1

*!

Calls: POPERROR() (function in POPERROR.PRG)

*1

FUNCTION yesno

PARAMETERS s row, s col, bx mess

PRIVATE s row, s col, bx mess, num lines, cur width, e mess

PRIVATE i, m col, yes on, temp, cur win, rvalue

```

```

yesno([<expN1>,[<expN2,]][<expC>])

*

Version # 2.2 FP

Date: 08-29-91

* Programmed by: Malcolm C. Rubel

*

* Copyright (c) 1990,91

* Performance Dynamics Associates

* All Rights Reserved

*

* Note: Function creates a dialog box in the middle of

* the screen, paints the message passed in <expC> and

* puts up two choices, "Yes" and "No", with "Yes" being

* the default. Function returns logical TRUE if the

* user selects "Yes", and FALSE if they select "No". The

* function returns TRUE if the user presses Ctrl + Enter

* no matter what prompt is currently selected.

* Modified 10-16-90 to make the mouse work properly.

* Function now uses no READ and no menu to get response.

* Modified 11-29-90 to add row and column movement.

* Modified 1-21-91 to take out macro expansion.

* Modified 7-20-91 to clear ON KEY LABELs with PUSH KEY

* CLEAR/POP KEY.

* Modified 8-29-91 to use WOUTPUT to control windows.

*****

*****

PUSH KEY CLEAR

```

rvalue = .F.

e mess = 'Invalid parameters passed to the function '+;

'YESNO. Function will return FALSE.'

cur\_win = WOUTPUT()

DO CASE

CASE PARAMETERS() = 0

&& no parameter passed

$s_row = 9$

s\_col = 16 bx mess = 'Your choice.....'

#### CASE PARAMETERS() = 1

```

IF TYPE('s_row') = 'C'

bx_mess = s_row

s_row = 9

s_col = 16

ELSE

```

```

IF TYPE('s_row') = 'N'

s_col = 16

bx_mess = 'Your choice.....'

ELSE

= poperror(e_mess)

POP KEY

RETURN(.F.)

ENDIF

```

**ENDIF**

```

CASE PARAMETERS() = 2

```

```

IF TYPE('s_row') = 'N' .AND. TYPE('s_col') = 'C'

bx_mess = s_col

s_col = 16

ELSE

```

```

IF TYPE('s_row') = 'N' .AND. TYPE('s_col') = 'N'

bx_mess = 'Your choice.....'

ELSE

= poperror(e_mess)

POP KEY

RETURN(.F.)

ENDIF

```

**ENDIF**

CASE PARAMETERS() = 3

```

IF TYPE('s_row') # 'N' .OR. TYPE('s_col') # 'N' .OR. ;

TYPE('bx_mess') # 'C'

= poperror(e_mess)

POP KEY

RETURN(.F.)

ENDIF

```

&& real bad parameters

```

OTHERWISE

= poperror(e_mess)

POP KEY

RETURN(.F.)

ENDCASE

```

cur width = SET('memowidth')

\*\*\* paint the message that is to appear at the top \*\*\* of the dialog box.

ENDIF

optcolor = SCHEME(2,6)&& for the option choiceshotcolor = SCHEME(2,7)&& for the hotkeys

\*\*\* make sure that everything fits on the screen!

```

s_row = IIF(s_row+5+num_lines<25,s_row,24-5-num_lines)

s_col = IIF(s_col<33,s_col,32)</pre>

```

DEFINE WINDOW yesno FROM s\_row,s\_col TO ; s\_row+5+num\_lines,s\_col+47 ; DOUBLE COLOR SCHEME 1 ACTIVATE WINDOW yesno

IF num\_lines = 1

(a) 01,03 SAY PADC(bx mess,40) i = 3ELSE FOR i = 1 TO num lines @ i,03 SAY MLINE(bx mess,i) **ENDFOR** i = i + 1**ENDIF** @ i,07 SAY CHR(174) + ' Yes '+ CHR(175) @ i,29 SAY '< No >' SET COLOR OF NORMAL TO (hotcolor) @ i,10 SAY 'Y' @ i,32 SAY 'N' SAVE SCREEN TO temp yes on = .T.&& starting condition KEY = 0DO WHILE .T. DO CASE CASE KEY = 151&& if mouse button pressed m col = MCOL()ลัยอัล DO CASE && not on right row CASE MROW() # i LOOP CASE BETWEEN(m col,7,15) && hit on yes rvalue = .T.**EXIT** CASE BETWEEN(m col,29,36) && hit on no rvalue = .F.

# St. Gabriel's Library, Au

EXIT

ENDCASE

\*\*\* test for right or left arrow keys and repaint

CASE KEY = 4 .OR. KEY = 19 yes on = IIF(yes on,  $F_{,,}T_{.}$ )

CASE KEY = 13 && Enter key pressed rvalue = IIF(yes\_on,.T.,.F.) EXIT

\*\*\* test for 'y', 'Y', and Ctrl + Enter

CASE KEY = 89 .OR. KEY = 121 .OR. KEY = 10 rvalue = .T. EXIT

CASE KEY = 78 .OR. KEY = 110 && 'N' or 'n' rvalue = .F. EXIT

ENDCASE

```

IF yes_on

SET COLOR OF NORMAL TO (optcolor)

@ i,08 SAY ' Yes '

ELSE

SET COLOR OF NORMAL TO (optcolor)

@ i,30 SAY ' No '

ENDIF

```

KEY = INKEY(0, hm')

&& wait for key or mouse

RESTORE SCREEN FROM \_temp

ENDDO

```

&& mouse hit

IF KEY = 151

RESTORE SCREEN FROM temp

SET COLOR OF NORMAL TO (optcolor)

IF rvalue

(a) i,07 SAY CHR(174) + 'Yes '+ CHR(175)

ELSE

@ i,29 SAY '< No >'

ENDIF

= INKEY(.3,'H')

ENDIF

SET MEMOWIDTH TO cur width

&& reset memowidth

SET COLOR OF NORMAL TO

RELEASE WINDOW yesno

IF EMPTY(cur win)

ACTIVATE SCREEN

ENDIF

POP KEY

RETURN(rvalue)

*: EOF: YESNO.PRG

*****

*:

*: Procedure file: C:\FOXPRO\ACLINE\POPERROR.PRG

*:

*:

System: Data Communictaion On Electric Line

Author: Cherdchai J(361-6310) Suvir K(361-6898)

*.

Copyright (c) 1998, ABAC EN 4902 Engineering Project II

*:

*: Last modified: 09/12/91

0:00

*:

*: Procs & Fncts: POPERROR()

*.

*.

Documented 03/15/98 at 17:22

FoxDoc version 2.10f

```

```

*!

*!

Function: POPERROR()

*!

Called by: BIGLETT()

*!

(function in BIGLETT.PRG)

: WEXPLODE()

*!

(function in WEXPLODE.PRG)

*1

: YESNO()

(function in YESNO.PRG)

*|

*†

Calls: BEEP()

(function in BEEP.PRG)

*|

FUNCTION poperror

PARAMETERS err mess

PRIVATE cur color, cur curs, bord str, err mess, say mess

PRIVATE num lines, start line, cur width, i, rvalue

PRIVATE cur win

*******

poperror(<expC>)

Version # 2.0 FP

Date: 07-20-91

* Programmed by: Malcolm C. Rubel

*

* Copyright (c) 1991

* Performance Dynamics Associates

* All Rights Reserved

* Note: Procedure pops up an error in lower right corner

* of screen and waits for a keypress to go back to screen.

* Modified 7-20-91 to include PUSH/POP kev.

*****

PUSH KEY CLEAR

= beep(1)

\operatorname{cur} \operatorname{win} = \operatorname{WOUTPUT}()

cur width = SET('memowidth')

&& save the old setting

SET MEMOWIDTH TO 48

```

num\_lines = MEMLINES(err\_mess) && how long is message?

55

start\_line = 20 - num\_lines && starting row for box

#### DEFINE WINDOW poperr FROM start\_line,14 TO 23,65 DOUBLE ; SHADOW COLOR SCHEME 19

ACTIVATE WINDOW poperr

\*\*\* paint the message on the screen line by line

```

IF num_lines = 1

@ 0,01 SAY PADC(err_mess,48)

i = 1

ELSE

```

```

FOR i = 0 TO num_lines-1

say_mess = MLINE(err_mess,i+1)

@ i,01 SAY LTRIM(say_mess) && say message line

ENDFOR

```

ENDIF

\*\*\* draw a line across the bottom of the message and \*\*\* paint "press any key..."

@ i,00 SAY REPLICATE(CHR(196),50) && draw line

@ i+1,01 SAY 'Press any key to continue....'

IF WEXIST('poperr') RELEASE WINDOW poperr ENDIF

IF EMPTY(cur\_win) ACTIVATE SCREEN ENDIF

SET MEMOWIDTH TO cur\_width

#### POP KEY

```

RETURN(rvalue)

*: EOF: POPERROR.PRG

*.

*: Procedure file: C:\FOXPRO\ACLINE\BEEP.PRG

*.

*.

System: Data Communication On Electric Line

*.

Author: Cherdchai J(361-6310) Suvir K(361-6898)

Copyright (c) 1998, ABAC EN 4902 Engineering Project II

*.

*: Last modified: 09/12/91

0:00

*:

*: Procs & Fncts: BEEP()

*.

*.

Documented 03/15/98 at 17:22

FoxDoc version 2.10f

*1

*1

Function: BEEP()

*1

(function in POPERROR.PRG)

*1

Called by: POPERROR()

*1

FUNCTION beep

PARAMETERS song

PRIVATE song, i

*****

beep(<expN>)

* Version # 1.0 FP

Date: 10-26-89

* Programmed by: Malcolm C. Rubel

*

* Copyright (c) 1988

Performance Dynamics Associates

* All Rights Reserved

*

Note: Plays the songs from the Xbase Hit Parade.

```

\* 1 = errorsong 2 = danger3 = hello4 = death5 = slide up6 = slide down\*\*\*\*\* \*\*\*\*\*\*\*\*\*\*\*\* IF TYPE('song') # 'N' && if bizzare thing passed song = 0**ENDIF** DO CASE CASE song = 1SET BELL TO 800,1 ?? CHR(7) = INKEY(.1) ?? CHR(7) CASE song = 2SET BELL TO 523.3,1 ?? CHR(7) = INKEY(.1) ?? CHR(7) =INKEY(.1) ?? CHR(7) = INKEY(.1) ?? CHR(7) = INKEY(.1) CASE song = 3SET BELL TO 261,3 ?? CHR(7) SET BELL TO 349,4 ?? CHR(7) SET BELL TO 440,1 ?? CHR(7) SET BELL TO 349,1

?? CHR(7) SET BELL TO 261,3 ?? CHR(7) SET BELL TO 349,4 ?? CHR(7) SET BELL TO 440,8 ?? CHR(7) SET BELL TO 349,6 ?? CHR(7) CASE song = 4SET BELL TO 261,8 ?? CHR(7) SET BELL TO 261,7 ?? CHR(7) SET BELL TO 261,2 ?? CHR(7) SET BELL TO 261,8 ?? CHR(7) SET BELL TO 311,7 ?? CHR(7) SET BELL TO 293,2 ?? CHR(7) SET BELL TO 293,7 ?? CHR(7) SET BELL TO 261,2 ?? CHR(7) SET BELL TO 261,7 ?? CHR(7) SET BELL TO 247,2 ?? CHR(7) SET BELL TO 261,8 ?? CHR(7) CASE song = 5FOR i = 400 TO 1800 STEP 100 SET BELL TO i,1

```

?? CHR(7)

```

ENDFOR

# St. Gabriel's Library, Au

```

CASE song = 6

FOR i = 1800 TO 400 STEP -100

SET BELL TO i,1

?? CHR(7)

ENDFOR

```

#### OTHERWISE SET BELL TO 440,6

```

?? CHR(7)

```

ENDCASE

```

RETURN(.T.)

*: EOF: BEEP.PRG

*.

*: Procedure file: C:\FOXPRO\ACLINE\UNTALK.PRG

*.

*.

System: Data Communictaion On Electric Line

*.

Author: Cherdchai J(361-6310) Suvir K(361-6898)

*.

Copyright (c) 1998, ABAC EN 4902 Engineering Project II

*: Last modified: 09/12/91

0:00

*.

*: Procs & Fncts: UNTALK()

*.

*.

Documented 03/15/98 at 17:22

FoxDoc version 2.10f

*1

*!

Function: UNTALK()

*1

*1

Called by: MAIN.PRG

*!

FUNCTION untalk

*

untalk()

```

- \* Version # 1.0 FP Date: 01-29-90

- \* Programmed by: Malcolm C. Rubel

- \*

- \* Copyright (c) 1990

- \* Performance Dynamics Associates

- \* All Rights Reserved

- \*

- \* Note: Function releases the window that was defined by

\* POPTALK.

```

******

```

IF WEXIST('pop\_talk') RELEASE WINDOW pop\_talk ENDIF

RETURN(") \*: EOF: UNTALK.PRG

## **AT89C51** Assembly Program

T I M E R . A S M Interfacing ICM7217CIPI & AT89C51 Microcontroller Displays Time Remaining In Hours And Minutes Hardware and Software Design By Suvir Kumar 3616898 and 3616310 Cherdchai Jungsatitkul Electronics and Electrical Engineering Project ASSUMPTION UNIVERSITY FACULTY OF ENGINEERING

#### ORG 0000H

;Starting Address

TMOD DATA 089H IE0 BIT 089H TLO DATA 08AH TH0 DATA 08CH TRO BIT 08CH P0 **DATA 080H** P1 **DATA 090H** P2 DATA 0A0H EX0 BIT 0A8H ETO BIT 0A9H EA BIT OAFH PSW DATA 0D0H ACC DATA 0E0H

SJMP START

ORG 0003H ACALL INT\_INT0 RETI

ORG 000BH ACALL INT\_TC0 (SOFTWARE) RETI

ORG 0045H START: ;Timer Mode ;Interrupt ;Timer 0 Low Byte ;Timer 0 High Byte ;Timer 0 Run Control ;Port 0 Dip Switch Port ;Port 1 Control HARRY Port ;Relay Driver Port ;External Interrupt ;Enable Timer 0 Interrupt ;External Interrupt Enable ;Program Status Word ;Accumulator

;Jump Straight Into Program Main Code Segment

;Address of Hardware Int ;Call Count Up Interrupt Service (HARDWARE) ;Return From Interrupt

;Address of Timer Int ;Call Count Down With Timing Interrupt

;Return From Interrupt

;Address Of Start ;Start

MOV R1,#0FFH D Ε ALAY1: MOV R2,#0FFH L DJNZ R2,\$ Α Υ DJNZ R1, ALAY1 MOV R1,#0FFH D ALAY2: Ε MOV R2,#0FFH L DJNZ R2,\$ А DJNZ R1, ALAY2 Y SETB P1.3 MOV R1,#0FFH ALAY3: MOV R2,#0FFH DJNZ R2,\$ **DJNZ R1, ALAY3 CLR P1.3** MOV R1,#0FFH ALAY4: MOV R2,#0FFH DJNZ R2,\$ **DJNZ R1, ALAY4** SETB P1.3 ;And Thou Shalt Remain High CLR ET0 ;Disable Timer Interrupt CLR TR0 Stop Timer 0 MOV 30H,#00H Clear Value In Address 30H Before Start MOV 31H,#00H Clear Value In Address 31H Before Start MOV 32H,#00H Clear Value In Address 32H Before Start MOV TMOD,#01H SI Set Timer Mode 1 (16 bit) MOV TL0,#000H Set Countdown MOV TH0,#090H Until 09000H ;Enable All External Interrupts SETB EA To Detect Falling Edge Of Interrupt SETB IE0 SETB EX0 ;Enable External Interrupt E1 ;Jump Up And Down Here Forever SJMP \$ INT INTO: Hardware Interrupt Service Procedure Push Accumulator **PUSH ACC PUSH PSW** ;Push Program Status Word

:D MOV R1,#0FFH ; E ALAY5: В MOV R2,#0FFH 0 DJNZ R2,\$ U **DJNZ R1, ALAY5** MOV R1,#0FFH Ν С ALAY6: E MOV R2,#0FFH DJNZ R2,\$ **DJNZ R1, ALAY6** :Enable Timer Interrupt SETB ET0 SETB TR0 :Start Timer 0 :Turn On Relay CLR P1.2 CLR A ;Clear Accumulator MOV 30H,#00H :Clear Address 30H Read Data From Dip Switch Into Acc MOV A,P0 :Move Dip Sw Value into 30H MOV 30H,A PULSER: Procedure To Generate Up Count Pulses ; D MOV R1,#050H E ALAY7: L MOV R2,#050H DJNZ R2.\$ Α Y **DJNZ R1, ALAY7** Set Harry To Count Up Mode **SETB P1.1** MOV R1,#050H D Ε ALAY8: MOV R2,#050H DJNZ R2,\$ A **DJNZ R1, ALAY8** Y **CLR P1.0** MOV R1,#050H ALAY9: MOV R2,#050H DJNZ R2,\$ DJNZ R1, ALAY9 SETB P1.0 MOV R1.#050H BLAY1: MOV R2,#050H DJNZ R2,\$ **DJNZ R1, BLAY1** And Thou Shalt Remain Low **CLR P1.0** ;Number Of Pulses To Be Sent **DJNZ 30H, PULSER** POP ACC ;Pop Value Of Accumulator :Pop Value Of Program Status Word POP PSW RET

INT\_TC0: PUSH ACC PUSH PSW

MOV A, P2

JZ ZERO\_DISP

COUNT\_DWN: MOV TL0,#00H MOV TH0,#90H MOV A,31H ADD A,#08 MOV 31H,A

CJNE A,#0F0H,FINISH MOV A,32H ADD A,#1 MOV 32H,A

CJNE A,#3CH,FINISH MOV 32H,#00 CLR P1.0 CLR P1.1 ;Software Interrupt Service Procedure ;Push Value Of Accumulator On To Stack ;Push Value Of Program Status Word On To Stack

;Check If 00.00 On Display

;Set Timer Count ;Down Until 0900EH ;Move Contents Of Memory Loc 31H into Acc ;Add Acc With 08 ;Move Contents Of Acc Back Into Memory Address 31H ;Conditional Jump If Not Equal To Finish... ;Move Contents Of Memory Loc 32H into Acc ;Add Acc With 01 ;Move Contents Of Acc Back Into Memory Address 32H ;Conditional Jump If Not Equal To Finish ;Clear The Adress Loc 32H ;Turn Off Count ;Set Count Down Mode

MOV R1,#0FFH BLAY2: MOV R2,#0FFH DJNZ R2,\$ DJNZ R1,BLAY2 CLR P1.0 MOV R1,#0FFH BLAY3: MOV R2,#0FFH DJNZ R2,\$ DJNZ R1,BLAY3 SETb P1.0 MOV R1,#0FFH BLAY4: MOV R2,#0FFH

I

1

A Y

ł

: !

DJNZ R2,\$ **DJNZ R1, BLAY4 CLR P1.0** MOV R1,#0FFH BLAY5: MOV R2,#0FFH DJNZ R2,\$ DJNZ R1, BLAY5 SJMP FINISH ZERO DISP: SETB P1.2 SETB P1.1 CLR ET0 CLR TR0 SETB P1.3 MOV R1,#0FFH BLAY6: MOV R2.#0FFH DJNZ R2,\$ **DJNZ R1, BLAY6 CLR P1.3** MOV R1,#0FFH BLAY7: MOV R2,#0FFH DJNZ R2,\$ DJNZ R1, BLAY7 SETB P1.3 CLR P1.0

FINISH: POP ACC POP PSW RET

END

;Turn Off Relay ;Make It Count Up Mode (SAFETY SAKE) ;Disable Timer Interupt ;Stop Timer 0

1

I

ļ

!

1

;! ;!

And Thou Shalt Remain High; Keep The COUNT OFF

1

AND THE FINISH LINE Pop Value Of Accumulator On To Stack Pop Value Of Program Status Word To Stack Return From Interrupt

;ABDE ABDE THATS ALL FOLKS!!

# Chapter 5