# An 80 MHz Wireless LAN (Physical Layer)

by

Sumet Assawapongkasem

Faculty of Engineering July 2000

132669

# An 80 MHz Wireless LAN (Physical Layer)

### A thesis

submitted to the Faculty of Engineering

Sumet Assawapongkasem

in partial fulfillment of the requirements for the degree of Master of Engineering in Broadband Telecommunications

#### Advisor: Dr. Thiraphong Charoenkhunwiwat

Assumption University Bangkok, Thailand July 2000

#### "An 80 MHz Wireless LAN (Physical Layer)"

by

#### Mr.Sumet Assawapongkasem

A Thesis submitted in partial fulfillment of the requirements for the degree of

Master of Engineering Majoring in Broadband Telecommunications

#### **Examination Committee:**

| 1. | Dr.Thiraphong | Charoenkhunwiwat | (Advisor) |

|----|---------------|------------------|-----------|

|    |               |                  |           |

2. Dr.Sudhiporn Patumtaewapibal (Member) Na Nacara 3. Dr.Wittawat (Member)

Angkaew

4. Dr.Tuptim

(MUA Representative)

Examined on: July 24, 2000 Approved for Graduation on: ...September 18, 2000

> Faculty of Engineering, Assumption University Bangkok, Thailand

#### **ABSTRACT**

A wireless LAN system is proposed to provide mobility for existing data communication services. This thesis presents a design of the wireless LAN card to transmit data at frequency of 80 MHz and receive data from MAC layer. Direct sequence spread spectrum and quadrature phase shift keying (QPSK) modulation technique are used in design. Filter and amplifier are used to increase the performance of the signal and reduce the noise, and this system supports a data rate up to 2 Mbps. The spread spectrum system design along with detailed description of hardware and software simulation is presented.

i

#### **ACKNOWLEDGEMENT**

I would like to thank my advisor, Dr. Thiraphong Charoenkhunwiwat, and my coadvisor, Dr. Wittawat Na Nacara, for his consistent advice, encouragement, and confidence. I am also very thankful to Dr. Sudhiporn Patumtaewapibal, Dean of the Faculty of Engineering, for giving valuable advice and supporting everything.

Thanks to Dr. Nick Marly, Former Director of Broadband Telecommunications, and Dr. Kittiphan Teachakittiroj, Acting Director of Broadband Telecommunications, for guiding and assisting me of making my thesis.

I also want to thank Mr. Myint Shwe for helping of my design and giving advice. I am also grateful to all my other friends and colleagues at the department of Broadband Telecommunications. I could not have completed this master's degree thesis without the help of these people.

I wish to express my sincerest appreciation to my parents, who understand and support me to finish my study. Finally I wish to thank all the people who have made this work possible. 🔺 2189739

### TABLE OF CONTENTS

|                                                 | Page |

|-------------------------------------------------|------|

| ABSTRACT                                        | i    |

| ACKNOWLEDGEMENT                                 | ii   |

| LIST OF FIGURES                                 | vii  |

| LIST OF TABLES                                  | ix   |

| CHAPTER 1 INTRODUCTION                          | 1    |

| 1.1 Objective VERS/                             | 1    |

| 1.2 History of Wireless Network                 | 1    |

| 1.3 Wireless Network Architecture               | 3    |

| 1.3.1 Logical Architecture of Wireless Network  | 3    |

| 1.3.2 Physical Architecture of Wireless Network | 5    |

| 1.3.2.1 End-User Appliances                     | 6    |

| 1.3.2.2 Network Software                        | 7    |

| 1.3.2.3 Wireless Network Software               | 8    |

| 1.3.2.4 Antenna                                 | 9    |

| 1.3.2.5 The Communication Channel               | 11   |

| 1.4 Radio-based Wireless LANs                   | 11   |

| 1.4.1 ISM Band                                  | 12   |

| 1.4.2 ISM Band Availability                     | 13   |

| 1.4.3 Narrow Band Modulation                    | 14   |

| 1.4.4 Spread Spectrum Modulation                | 15   |

| 1.4.5 Radio Signal Interference                 | 16   |

| 1.4.5.1 Inward Interference                     | 16   |

| 1.4.5.2 Outward Interference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 17  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 1.4.5.3 Technique for Reducing Interference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 17  |

| 1.5 Benefits of Wireless Networks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 18  |

| 1.5.1 Mobility                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 18  |

| 1.5.2 Installation in Difficult-to-Wire Areas                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 19  |

| 1.5.3 Reduced Installation Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 20  |

| 1.5.4 Increased Reliability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 20  |

| 1.5.5 Long-Term Cost Savings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 21  |

| 1.6 The Future of Wireless Networks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 21  |

| CHAPTER 2 Theory of DSSS and QPSK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 23  |

| 2.1 Spread Spectrum                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 23  |

| 2.1.1 How Spread Spectrum Works                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 23  |

| 2.1.2 More Details on Spread Spectrum                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 24  |

| <ul> <li>1.4.5.3 Technique for Reducing Interference</li> <li>1.5 Benefits of Wireless Networks <ol> <li>1.51 Mobility</li> <li>2.2 Installation in Difficult-to-Wire Areas</li> <li>3.3 Reduced Installation Time</li> <li>3.4 Increased Reliability</li> <li>3.5 Long-Term Cost Savings</li> </ol> </li> <li>1.6 The Future of Wireless Networks</li> <li>2.16 The Future of Wireless Networks</li> <li>2.19 Spread Spectrum</li> <li>2.11 How Spread Spectrum Works</li> <li>2.12 More Details on Spread Spectrum</li> <li>2.13 Direct Sequence Spread Spectrum</li> <li>2.14 Frequency Hopping Spread Spectrum</li> <li>2.15 Direct Sequence vs Frequency Hopping</li> <li>2.15.1 The Basics</li> <li>2.15.2 Comparisons</li> <li>2.15.3 Summary</li> <li>2.2 Modulation</li> <li>2.2 QPSK Modulation</li> <li>2.3 Transmitting Data Using QPSK</li> <li>3.3 The IEEE 802.11 Wireless Standard</li> </ul> | 26  |

| 2.1.4 Frequency Hopping Spread Spectrum                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 29  |

| 2.1.5 Direct Sequence vs Frequency Hopping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 31  |

| 2.1.5.1 The Basics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 31  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 34  |

| 2.1.5.3 Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 36  |

| 2.2 Modulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 37  |

| 2.2.1 Type of Modulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | .37 |

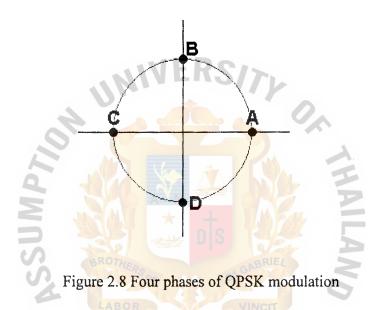

| 2.2.2 QPSK Modulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 38  |

| 2.2.3 Transmitting Data Using QPSK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 38  |

| 2.3 The IEEE 802.11 Wireless Standard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 40  |

| 2.3.1 IEEE 802.11 Physical Layer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 40  |

| 2.3.2 Direct Sequence Spread Spectrum Physical Layer | 40  |

|------------------------------------------------------|-----|

| 2.3.3 IEEE 802.11 MAC Layer                          | 41  |

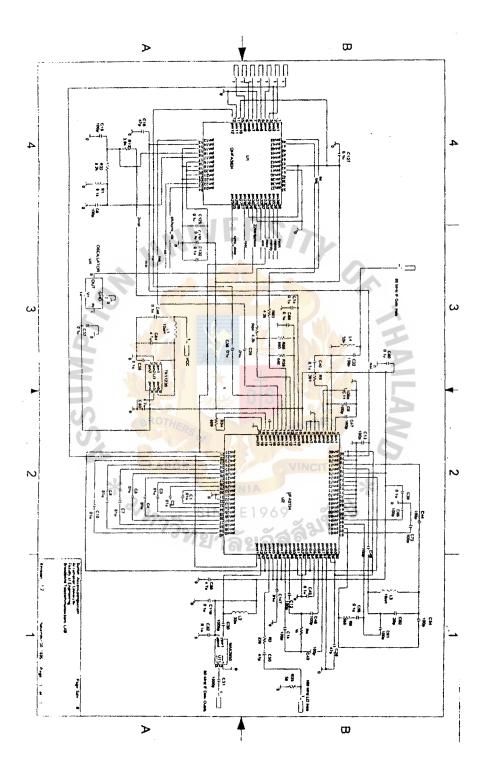

| CHAPTER 3 Circuit Diagram and Description            | 42  |

| 3.1 Overview                                         | 42  |

| 3.2 General Specification                            | 42  |

| 3.3 Circuit Diagram and PCB Layout                   | 43  |

| 3.3.1 Transmit Processing                            | 45  |

| 3.3.2 Receive Processing                             | 46  |

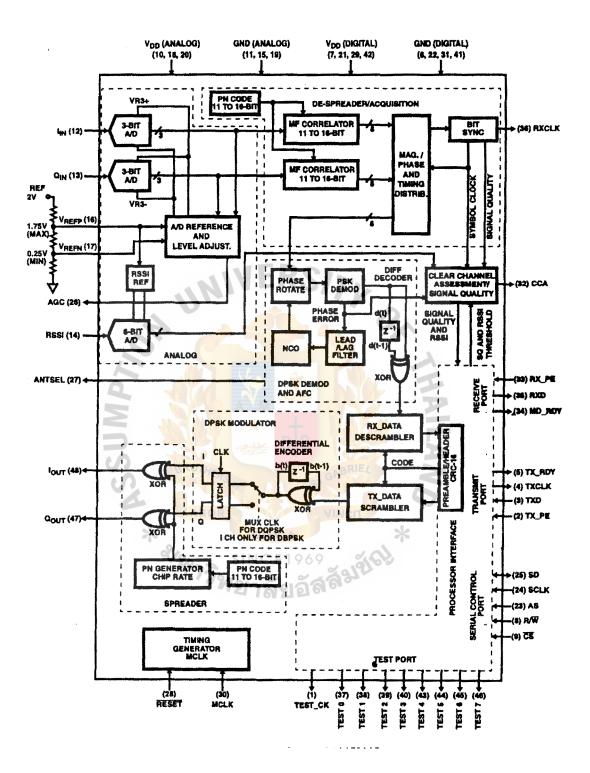

| 3.4 HFA3824 DSSS Baseband Processor                  | 48  |

| 3.4.1 Features                                       | 48  |

| 3.4.2 Description                                    | 52  |

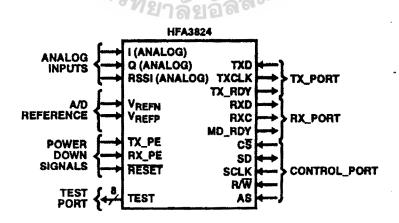

| 3.4.3 External Interfaces Description                | 52  |

| 3.4.3.1 Control Port                                 | .53 |

| 3.4.3.2 TX Port                                      | 54  |

| 3.4.3.3 RX Port                                      | 56  |

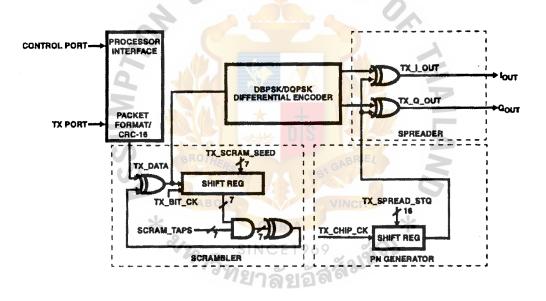

| 3.4.4 Transmitter Description                        | 57  |

| 3.4.5 Header/Packet Description                      | 58  |

| 3.4.6 Receiver Description                           | 60  |

| 3.5 HFA3724 400MHz Quadrature IF Mod/Demod           | 62  |

| 3.5.1 Features                                       | 62  |

| 3.5.2 Description                                    | 66  |

| 3.5.3 Overall Device Description                     | 67  |

| CHAPTER 4 Simulation and Measurement                 |     |

| 4.1 Simulation                                       | 70  |

| 4.1.1 Matlab Simulation                              | 70  |

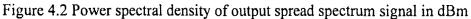

| 4.1.2 Ansoft Simulation    | 72 |

|----------------------------|----|

| 4.2 Measurement            | 76 |

| 4.3 Comparisons            | 80 |

| CHAPTER 5 Conclusion       | 81 |

| APPENDIX A Components List | 83 |

| APPENDIX B Matlab Program  | 84 |

| BIBILOGRAPHY               | 85 |

### LIST OF FIGURES

| Figure |                                                              | Page |

|--------|--------------------------------------------------------------|------|

| 1.1    | The Open System Interconnection Reference Model              | 4    |

| 1.2    | The Wireless Network Logical Architecture                    | 5    |

| 1.3    | The Physical Components of a Wireless Network                | 6    |

| 1.4    | The Server-Based Network Operating System                    | 7    |

| 1.5    | The Operation of Carrier Sense Protocol                      | 9    |

| 1.6    | The Omidirectional vs Directional Antennas                   | 10   |

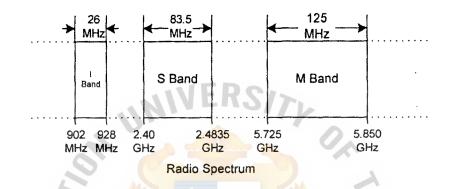

| 1.7    | The Industrial, Scientific, and Medical (ISM) Frequency Band | 13   |

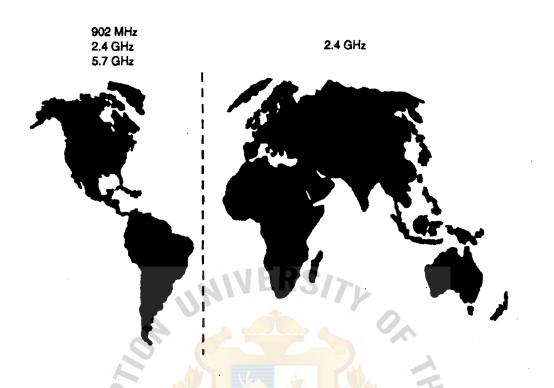

| 1.8    | ISM Spectrum Availability                                    | 14   |

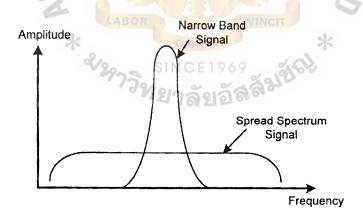

| 1.9    | Narrow Band vs Spread Spectrum Modulation                    | 15   |

| 1.10   | Inward and Outward Interference                              | 16   |

| 1.11   | A Difficult-to-wire Situation                                | 19   |

| 1.12   | The Future of Wireless Networking                            | 22   |

| 2.1    | The Operation of Direct Sequence Spread Spectrum             | 27   |

| 2.2    | Direct-Sequence Transmitter                                  | 28   |

| 2.3    | Generation of PN Signals                                     | 28   |

| 2.4    | A Frequency Hopping Spread Spectrum                          | 30   |

| 2.5    | Spreading of Direct Sequence Signal                          | 32   |

| 2.6    | Despreading of Direct Sequence Signal                        | 33   |

| 2.7    | Frequency Hopping Signal                                     | 34   |

| 2.8    | Four Phases of QPSK Modulation                               | 38   |

| 2.9    | Example of QPSK Modulation                                   | 39   |

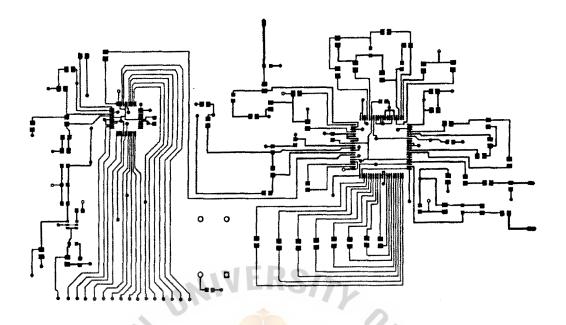

| 3.1    | Circuit Design Diagram                                       | 43   |

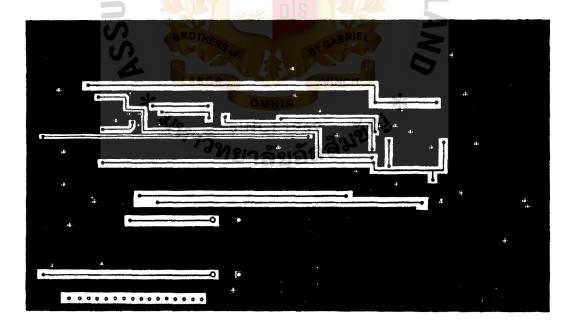

| 3.2  | PCB Design (Front Side)                                 | 44 |

|------|---------------------------------------------------------|----|

| 3.3  | PCB Design (Back Side)                                  | 44 |

| 3.4  | Circuit Diagram of HFA3824                              | 49 |

| 3.5  | External Interface                                      | 52 |

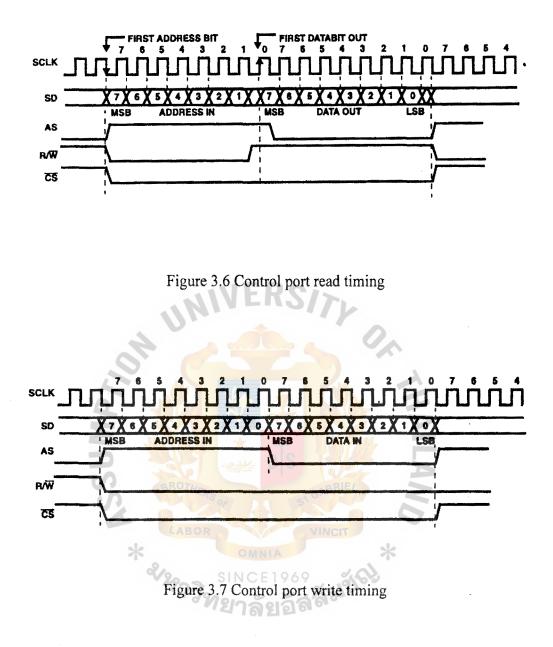

| 3.6  | Control Port Read Timing                                | 54 |

| 3.7  | Control Port Write Timing                               | 54 |

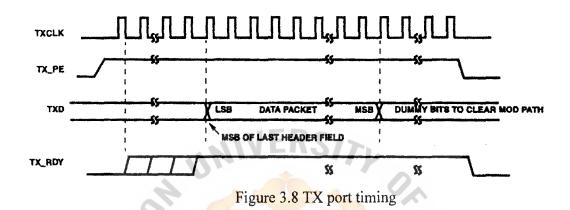

| 3.8  | TX Port Timing                                          | 55 |

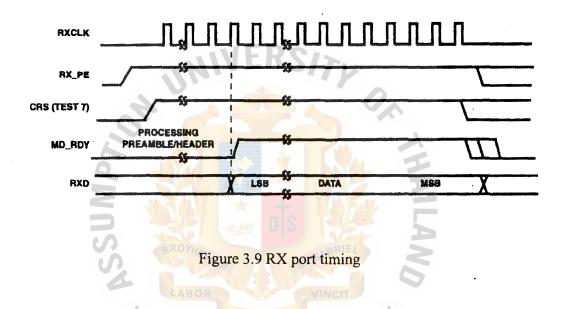

| 3.9  | RX Port Timing                                          | 56 |

| 3.10 | Modulator Diagram                                       | 57 |

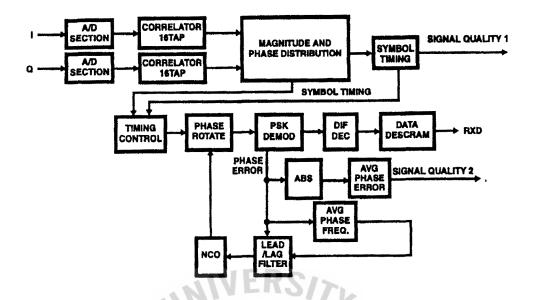

| 3.11 | Demodulator Diagram                                     | 61 |

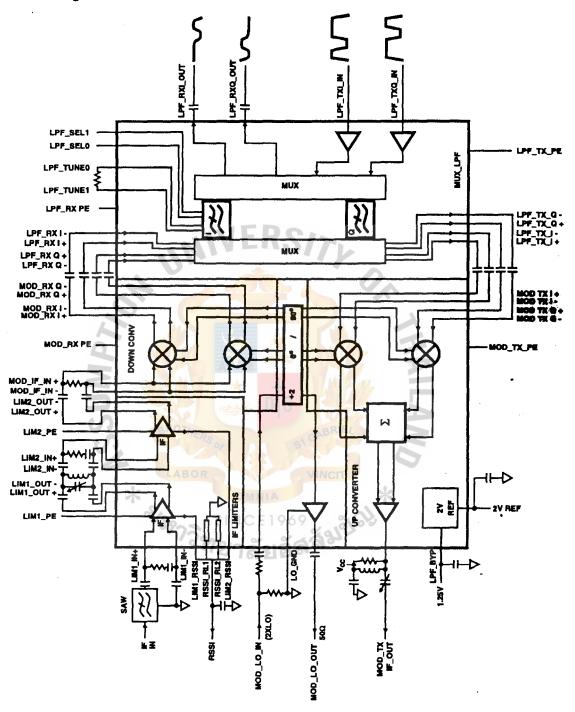

| 3.12 | Circuit Diagram of HFA3724                              | 63 |

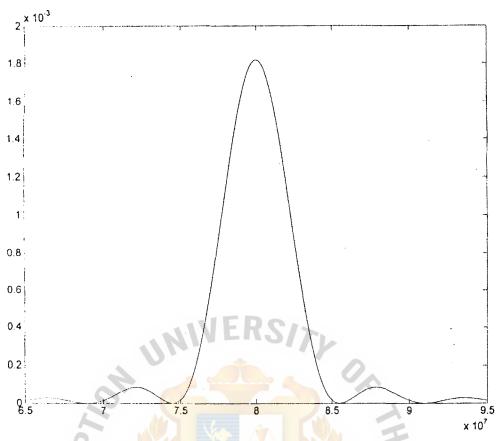

| 4.1  | Power Spectral Density of Output Spread Spectrum Signal | 71 |

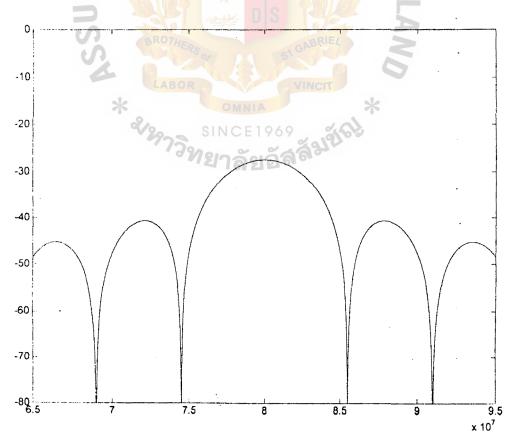

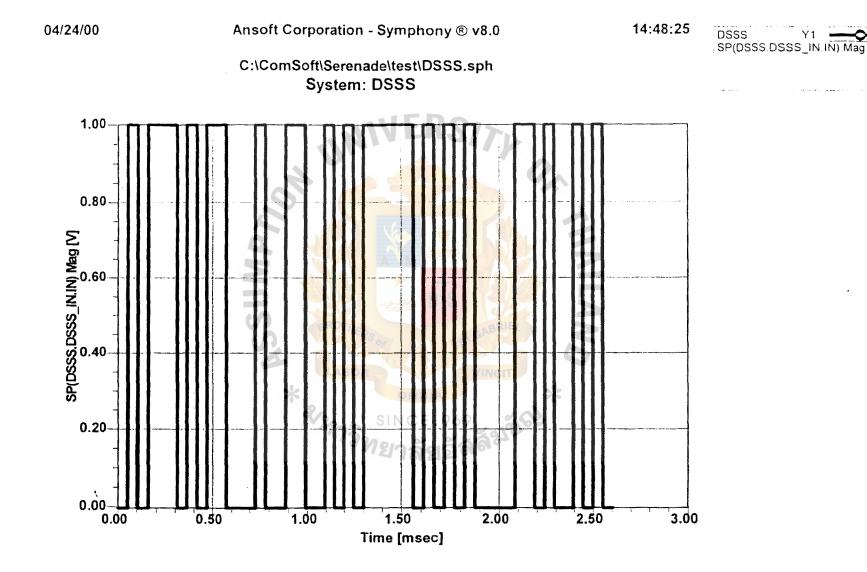

| 4.2  | Power of Output Spread Spectrum Signal in dBm           | 71 |

| 4.3  | A Simulation Circuit                                    | 73 |

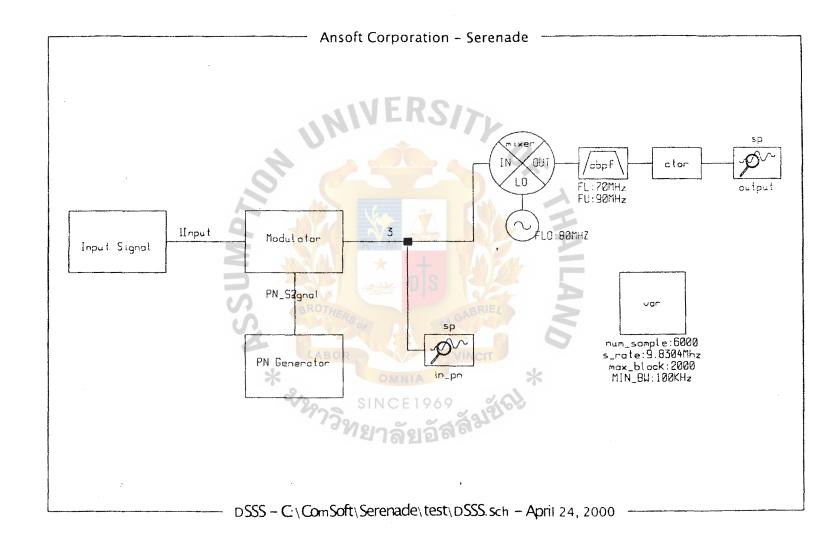

| 4.4  | Graph of Input Signal                                   | 74 |

| 4.5  | Graph of Output Signal Spectrum at 80 MHz               | 75 |

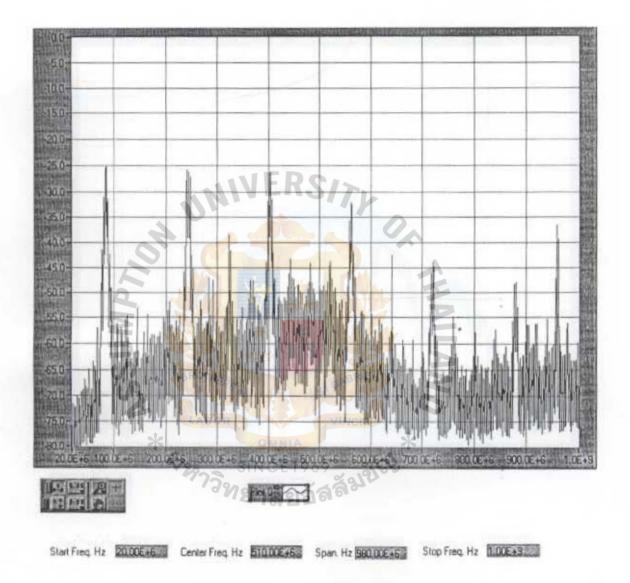

| 4.6  | Output Spectrum Signal with 1 GHz BW                    | 77 |

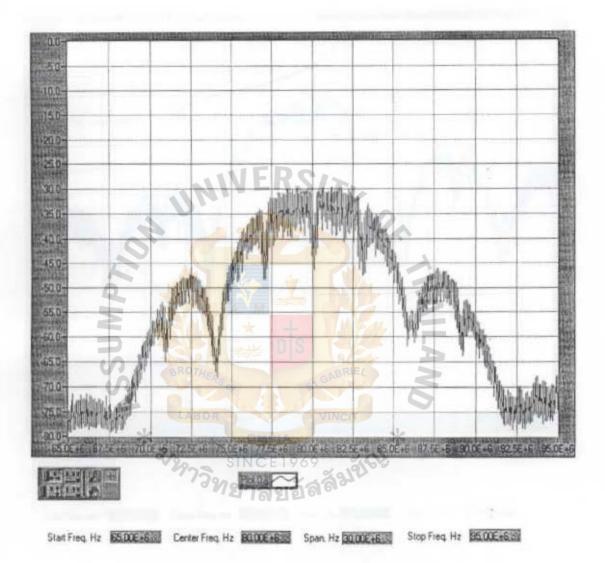

| 4.7  | Output Spread Spectrum Signal with 30 MHz BW            | 78 |

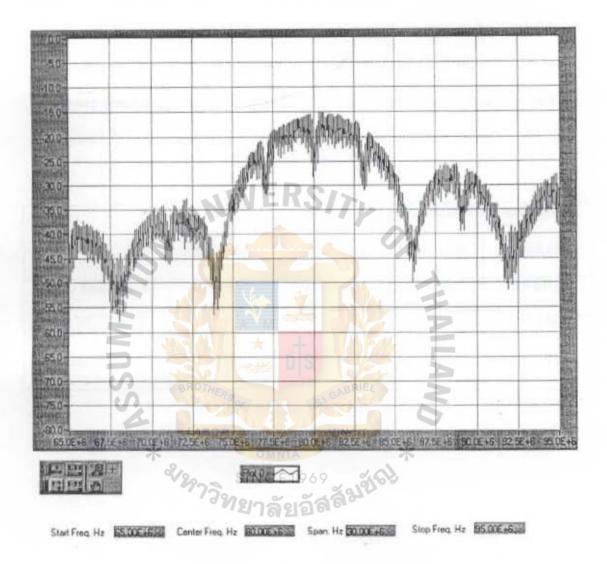

| 4.8  | Output Spread Spectrum Signal After Add Amplifier       | 79 |

### LIST OF TABLES

| Table |                                                                                                               | Page |

|-------|---------------------------------------------------------------------------------------------------------------|------|

| 2.1   | Comparison of DSSS & FHSS                                                                                     | 36   |

| 2.2   | Relationship Between Phase Changes and Dibits                                                                 | 39   |

| 2.3   | Phase Transition to Dibit                                                                                     | 39   |

| 3.1   | Pin Description of HFA3824                                                                                    | 50   |

| 3.2   | Pin Description of HFA3724                                                                                    | 64   |

| 4.1   | Comparison of Simulation and Measurement                                                                      | 80   |

| A.1   | The Components List                                                                                           | 82   |

|       | ROTHERS OF SIGNARIEL<br>ROTHERS OF SIGNARIEL<br>LABOR VINCT<br>* OMNIA<br>* SINCE1969<br>SINCE1969<br>MEIABOR |      |

.

#### **CHAPTER 1. INTRODUCTION**

In this chapter, we introduce to wireless system. Objective of this thesis and several information of wireless network are discussed. History of wireless network, wireless network architecture, radio-based wireless LAN, benefits of wireless networks, and the future of wireless network are discussed.

#### 1.1 Objective

Today, communication has increasing influence on our daily life. Wireless data communication services are widely used and allow people to access the data network without a physical connection. In this thesis, we want to design and build a real wireless LAN system operating at radio frequency of 80 MHz. The physical layer of this network has been designed to perform direct sequence spread spectrum processing and use technique of QPSK modulation to have a transmission rate up to 2 Mbps.

NIVERS/7L

#### **1.2 History of Wireless Networks**

The first indication of wireless networking dates back to the 1800s and earlier. Indians, for example, sent information to each other via smoke signals from a burning fire. Prior to the nineteenth century, scientists thought light was the only wavelength component of the electromagnetic spectrum. During the nineteenth and twentieth centuries, researchers learned that the spectrum actually consists of longer wavelengths (lower frequencies) as well. Experiments showed that lower frequencies, such as radio waves and infrared light, could be sent through the air with moderate amounts of transmit power and easy-to-manufacture antennas. As a result, companies began building radio

transmitters and receivers, making public and private radio communications, television, and wireless networking possible.

Network technologies and radio communications were brought together for the first time in 1971 at the University of Hawaii as a research project called ALOHANET. The ALOHANET system enabled computer sites at seven campuses spread out over four islands to communicate with the central computer on Oahu without using existing, unreliable, expensive phone lines. ALOHANET offered bi-directional communications, in a star topology, between the central computer and each of the remote stations. The remote stations had to communicate with each other via the centralized computer. ALOHANET became popular among network researchers because of the unique combination of packet switching and broadcast radio.

In 1985, the Federal Communications Commission (FCC) made the commercial development of radio-based LAN components possible by authorizing the public use of the Industrial, Scientific, and Medical (ISM) bands. This band of frequencies resides between 902 MHz and 5.85 GHz, just above the cellular phone operating frequencies. The ISM band is very attractive to wireless network vendors because it provides a part of the spectrum upon which to base their products, and end users do not have to obtain FCC licenses to operate the products. The ISM band allocation has had a dramatic effect on the wireless industry, prompting the development of wireless LAN components.

During the late eighties, the decreasing size of computers from desktop machines to laptops allowed employees to take their computers with them around the office and on business trips. Computer companies then scrambled to develop products that would support wireless connectivity methods. The current depressed state of the wireless LAN market should change as standards mature. The Institute of Electrical and Electronic Engineers (IEEE) 802 Working Group, responsible for the development of

LAN standards such as ethernet and token ring, initiated the 802.11 Working Group to develop a standard for wireless LANs.

#### **1.3 Wireless Network Architecture**

In general, networks perform many functions to transfer information from source to destination.

- The medium provides a bit pipes (path for data to flow) for the transmission of data.

- Medium access techniques facilitate the sharing of a common medium.

- Synchronization and error control mechanisms ensure that each link transfers the data intact.

- Routing mechanisms move the data from the originating source to the intended destination.

A good way to depict these functions is to specify the network's architecture. This architecture describes the protocols, major hardware, and software elements that constitute the network. A network architecture, whether wireless or wired, may be viewed in two ways, logically and physically.

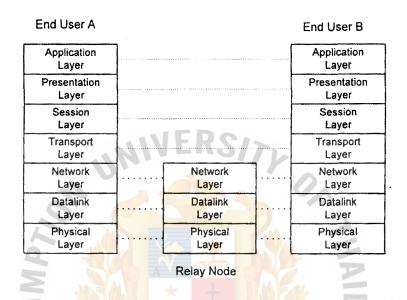

#### 1.3.1 Logical Architecture of a Wireless Network

A logical architecture defines the network's protocols—rules by which two entities communicate.

One popular standard logical architecture is the 7-layer Open System Interconnection (OSI) Reference Model, developed by the International Standards Organization (ISO). OSI specifies a complete set of network functions, grouped into layers. Figure 1.1 illustrates the OSI Reference Model.

Figure 1.1 The Open System Interconnection Reference Model

The OSI layers provide the following network functionality:

- Layer 7—Application layer. Establishes communications with other users and provides services such as file transfer and e-mail to the end users of the network.

- Layer 6—Presentation layer. Negotiates data transfer syntax for the application layer and performs translations between different data types, if necessary.

- Layer 5—Session layer. Establishes, manages, and terminates sessions between applications.

- Layer 4—Transport layer. Provides mechanisms for the establishment, maintenance, and orderly termination of virtual circuits, while shielding the higher layers from the network implementation details.

- Layer 3—Network layer. Provides the routing of packets from source to destination.

- Layer 2—Data Link layer. Ensures synchronization and error control between two entities.

- Layer 1—Physical layer. Provides the transmission of bits through a communication channel by defining electrical, mechanical, and procedural specifications.

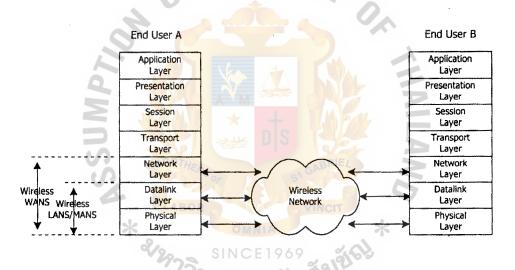

Wireless network logical architecture as shown in figure 1.2, wireless LANs and MANs function only within the Physical and Data Link layers, which provide the medium, link synchronization, and error control mechanisms. Wireless WANs provide these first two layers, as well as Network Layer routing.

Figure 1.2 The wireless network logical architecture

#### **1.3.2 Physical Architecture of a Wireless Network**

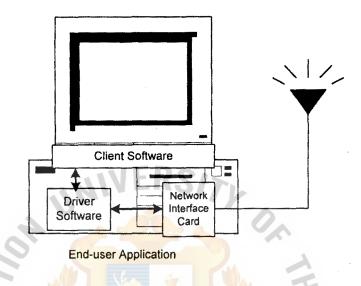

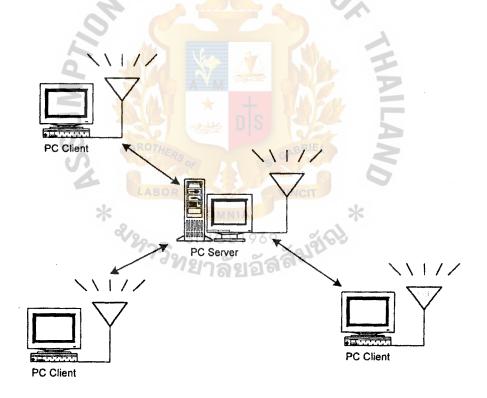

The physical components of a wireless network implement the Physical, Data Link, and Network Layer functions (see figure 1.3). The Network Operating System (NOS) of a network, such as Novell NetWare, supports the shared use of applications, printers, and disk space. The NOS, located on client and server machines, communicates with the wireless Network Interface Card (NIC) via driver software, enabling applications to utilize the wireless network for data transport. The NIC prepares data signals for propagation from the antenna through the air to the destination comprised of the same set of components.

Figure 1.3 The physical components of a wireless network

#### 1.3.2.1 End-User Appliances

As with any system, there must be a way for users to interface with applications and services. Whether the network is wireless or wired, an end-user appliance is a visual interface between the user and the network.

Following are the classes of user appliances:

- Desktop workstations

- Laptops

- Palmtops

- Pen-based computers

- Personal Digital Assistants (PDA)

- Pagers

#### 1.3.2.2 Network Software

A wireless network supports the NOS and its applications, such as word processing, databases, and e-mail, enabling the flow of data between all components. NOSs provide file and print services, acting as a platform for user applications. Many NOSs are server-oriented, as shown in figure 1.4, where the core software resides on a high-performance PC. A client, located on the end user's appliance, includes server software that directs the user's command to the local computer resources, or puts it out onto the network to another computer. Some wireless networks may also contain middleware that interfaces mobile applications to the wireless network hardware.

Figure 1.4 The server-based network operating system

#### 1.3.2.3 Wireless Network Interface

Computers process information in digital form, with low direct current (DC) voltages representing data ones and zeros. These signals are optimum for transmission within the computer, not for transporting data through wired or wireless media. A wireless network interface couples the digital signal from the end-user appliance to the wireless medium, which is air, to enable an efficient transfer of data between sender and receiver. This process includes the modulation and amplification of the digital signal to a form acceptable for propagation to the receiving location. *Modulation* is the process of translating the baseband digital signal to a suitable analog form. The wireless modulator translates the digital signal to a frequency that propagates well through the atmosphere. Wireless networks employ modulation by using radio waves and infrared light. *Amplification* raises the amplitude of the signal so it will propagate a greater distance.

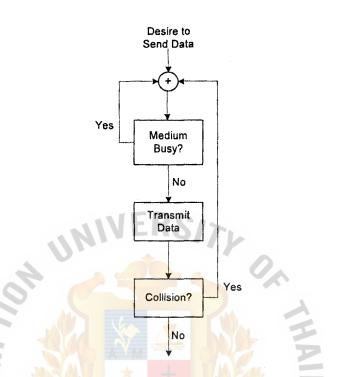

The wireless network interface also manages the use of the air through the operation of a communications protocol. For synchronization, wireless networks employ a carrier sense protocol similar to the common ethernet standard. This protocol enables a group of wireless computers to share the same frequency and space. As an analogy, consider a room of people engaged in a single conversation in which each person can hear if someone speaks. This represents a fully connected bus topology (where everyone communicates using the same frequency and space) that ethernet and wireless networks, especially wireless LANs, utilize. To avoid having two people speak at the same time, you should wait until the other person has finished talking. Also, no one should speak unless the room is silent. This simple protocol ensures only one person speaks at a time, offering a shared use of the communications medium. Wireless networks use carrier sense protocols and operate in a similar fashion, except the

communications are by way of radio signals or infrared light. Figure 1.5 illustrates the generic carrier sense protocol.

Figure 1.5 The operation of the carrier sense protocol

Wireless networks handle error control by having each station check incoming data for altered bits. If the destination station does not detect errors, it sends an acknowledgment back to the source station. If the station detects errors, the data link protocol ensures that the source station resends the packet.

#### 1.3.2.4 Antenna

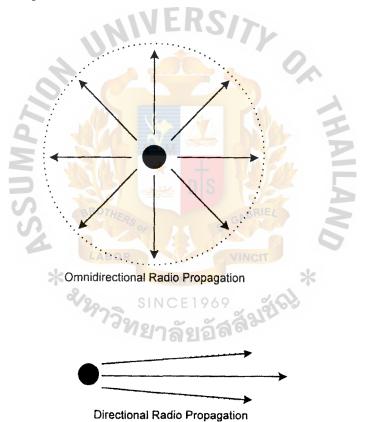

The antenna radiates the modulated signal through the air so that the destination can receive it. Antennas come in many shapes and sizes and have the following specific electrical characteristics:

• Propagation pattern

- Radiation power

- Gain

- Bandwidth

The propagation pattern of an antenna defines its coverage. A truly omnidirectional antenna transmits its power in all directions, whereas a directional antenna concentrates most of its power in one direction. Figure 1.6 illustrates the differences. Radiation power is the output of the radio transmitter. Most wireless network devices operate at less than 5 watts of power.

Figure 1.6 The omnidirectional versus directional antennas

A directional antenna has more gain (degree of amplification) than the omnidirectional type and is capable of propagating the modulated signal farther because it focuses the power in a single direction. The amount of gain depends on the directivity

of the antenna. An omnidirectional antenna has a gain equal to one; that is, it doesn't focus the power in any particular direction. A directional antenna, however, is considered to add gain (amplification) to the signal in certain directions.

#### 1.3.2.5 The Communications Channel

All information systems employ a communications channel along which information flows from source to destination. Ethernet networks may utilize twisted-pair or coaxial cable. Wireless networks use air as the medium. At the earth's surface, where most wireless networks operate, pure air contains gases such as nitrogen and oxygen. This atmosphere provides an effective medium for the propagation of radio waves and infrared light. Rain, fog, and snow, however, can increase the amount of water molecules in the air and can cause significant attenuation to the propagation of modulated wireless signals. Smog clutters the air, adding attenuation to the communications channel as well. *Attenuation* is the decrease in the amplitude of the signal, and it limits the operating range of the system. The ways to combat attenuation are to either increase the transmit power of the wireless devices, which in most cases is limited by the FCC, or to incorporate special amplifiers called repeaters that receive attenuated signals, amplify them, and transmit downline to the end station or next repeater.

#### 1.4 Radio-based Wireless LANs

The most widely sold wireless LAN products use radio waves as a medium between computers and peripherals. An advantage of radio waves over other forms of wireless connectivity is that they propagate through walls and other obstructions with fairly little attenuation. Even though several walls might separate the user from the server or

wireless bridge, users can maintain connections to the network—supporting true mobility. With radio-LAN products, a user with a portable computer can move freely through the facility while accessing data from a server or running an application.

A disadvantage of using radio waves, however, is that an organization must manage the radio waves along with other electromagnetic propagation. Medical equipment and industrial components utilize the same radio frequencies as wireless LANs, which could cause interference. An organization must determine whether potential interference is present before installing a radio-based LAN. Because radio waves penetrate walls, security may also be a problem. Unauthorized people from outside the controlled areas could receive sensitive information. However vendors often scramble the data signal to protect the information from being understood by inappropriate people.

This section discusses the following radio-based wireless LAN topics:

- ISM bands

- ISM Band Availability

- Narrow band wireless LANs

- Spread spectrum wireless LANs

- Radio signal interference

#### 1.4.1 ISM Bands

In 1985, as an attempt to stimulate the production and use of wireless network products, the FCC modified Part 15 of the radio spectrum regulation, which governs unlicensed devices. The modification authorized wireless network products to operate in the Industrial, Scientific, and Medical (ISM) bands. The ISM frequencies are shown in figure 1.7. The FCC allows users to operate wireless products without obtaining FCC licenses if the products meet certain requirements, such as operation under 1 watt

transmitter output power. This deregulation of the frequency spectrum eliminates the need for user organizations to perform costly and time-consuming frequency planning to coordinate radio installations that will avoid interference with existing radio systems. As you can see, more bandwidth is available within the higher frequency bands, which will support higher data rates.

Figure 1.7 The Industrial, Scientific, and Medical (ISM) frequency bands

#### 1.4.2 ISM Band Availability

The ISM band frequencies are not available in all parts of the world, limiting the capability to operate wireless products sold in the United States. Figure 1.8 identifies those countries that allow wireless LAN operation in the 902 MHz and 2.4 GHz ISM bands. The 2.4 GHz is the only unlicensed band available worldwide. This band was approved in North and South America in the mid-1980s and was accepted in Europe and Asia in 1995. Companies first began developing products in the 902 MHz band because manufacturing costs in this band were cheaper. The lack of availability of this band in some areas and the need for greater bandwidth, however, drove these companies to migrate many of their products to the 2.4 GHz band.

Figure 1.8 ISM spectrum availability

#### 1.4.3 Narrow Band Modulation

Conventional radio systems, such as television and AM/FM radio, utilize narrow band modulation. These systems concentrate all their transmit power within a narrow range of frequencies, making efficient use of the radio spectrum in terms of frequency space. The idea behind most communications design is to conserve as much bandwidth as possible; therefore, most transmitted signals utilize a relatively narrow slice of the radio frequency spectrum. Other systems using the same transmit frequency, however, will cause a great deal of interference because the noise source will corrupt most of the signal. To avoid interference, the FCC requires users of narrow band systems to obtain FCC licenses to properly coordinate the operation of radios. Narrow band products thus have a strong advantage because you can be fairly assured of operating without

interference. If interference does occur, the FCC will resolve the matter. This makes narrow band modulation good for longer links covering the geographical size of a metropolitan area.

#### 1.4.4 Spread Spectrum Modulation

l

Products that operate according to Part 15.247 of the FCC's Rules and Regulations must utilize spread spectrum modulation. What is spread spectrum? Spread spectrum modulation "spreads" a signal's power over a wider band of frequencies (see figure 1.9). This contradicts the desire to conserve frequency bandwidth, but the spreading process makes the data signal much less susceptible to electrical noise than conventional radio modulation techniques. Other transmission and electrical noise, typically narrow in bandwidth, will only interfere with a small portion of the spread spectrum signal, resulting in much less interference and less errors when the receiver demodulates the signal.

Figure 1.9 Narrow band versus spread spectrum modulation

Spread spectrum modulators use one of two methods to spread the signal over a wider area: direct sequence or frequency hopping.

#### 1.4.5 Radio Signal Interference

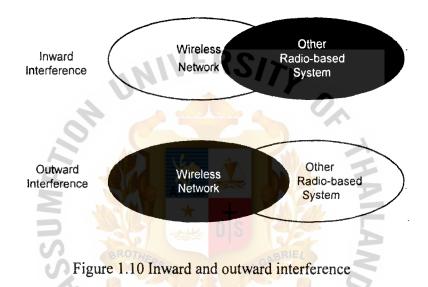

The purpose of radio-based networks is to transmit and receive signals efficiently over airwaves. This process, though, makes these systems vulnerable to atmospheric noise and transmissions from other systems. In addition, these wireless networks could interfere with other radio wave equipment. As shown in figure 1.10, interference may be inward or outward.

#### 1.4.5.1 Inward Interference

Most of us have experienced radio signal interference while talking on a wireless telephone, watching television, or listening to a radio. Someone close by might be communicating with another person via a short-wave radio system, causing harmonic frequencies that you can hear while listening to your favorite radio station. Or, a remote control car can cause static on a wireless phone while you are attempting to have a conversation. These types of interference might also disturb radio-based wireless networks in the form of inward interference. Interference with radio-based networks is not as bad as it might seem. The products using the ISM bands incorporate spread spectrum modulation that limits the amount of damage an interfering signal causes. The spread spectrum signal covers a wide amount of bandwidth, and a typical narrow bandwidth interference only affects a small part of the information signal, resulting in few or no errors. Thus, spread spectrum-type products are highly resistant to interference. Narrowband interference with signal-to-interference ratios of less than 10 dB does not usually affect a spread spectrum transmission. Wideband interference, however, can have damaging effects on any type of radio transmission. The primary source of wideband interference is domestic microwave ovens that operate in the 2.4 GHz band.

#### 1.4.5.2 Outward Interference

Inward interference is only half of the problem. The other half of the issue, outward interference, occurs when a wireless network's signal disrupts other systems, such as adjacent wireless LANs, navigation equipment on aircraft, and so on. This disruption results in the loss of some or all of the system's functionality. Interference is uncommon with ISM band products because they operate on such little power. The transmitting components must be very close and operating in the same bandwidth for either one to experience inward or outward interference.

#### 1.4.5.3 Techniques for Reducing Interference

When dealing with interference, you will want to coordinate the operation of radiobased wireless network products with your company's frequency management organization, if one exists. This will avoid potential interference problems.

Another tip, especially if no frequency management organization exists within your company, is to run some tests to determine the propagation patterns within your building. These tests let you know if existing systems may interfere with, and thus block and cause delay to, your network. You will also discover whether your signal will disturb other systems.

#### **1.5 Benefits of Wireless Networks**

Companies can realize the following benefits by implementing wireless networks:

- Mobility

- Ease of installation in difficult-to-wire areas

- Reduced installation time

- Increased reliability

- Long-term cost savings

#### 1.5.1 Mobility

User mobility indicates constant physical movement of the person and their network appliance. Many jobs require workers to be mobile, such as inventory clerks, healthcare workers, policemen, emergency care specialists, and so on. Wireline networks require a physical tether between the user's workstation and the network's resources, which makes access to these resources impossible while roaming about the building or elsewhere. As an analogy, consider talking on a wired phone having a cord connecting the handset to the telephone base station. You can utilize the phone only within the length of its cord. With a wireless cellular phone, however, you can walk freely within your office, home, or even talk to someone while driving a car. Wireless networking offers mobility to its users much like the wireless phone, providing a constant connection to information on the network.

#### 1.5.2 Installation in Difficult-to-Wire Areas

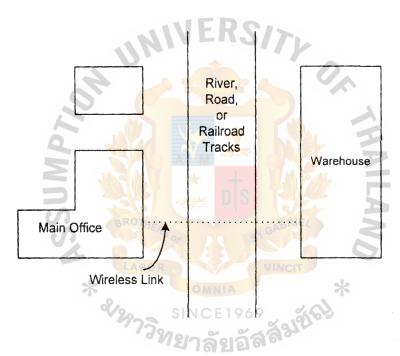

The implementation of wireless networks offers many tangible cost savings when performing installations in difficult-to-wire areas. If rivers, freeways, or other obstacles separate buildings you want to connect (see figure 1.11).

Figure 1.11 A difficult-to-wire situation

In some cases, it might be impossible to install cabling. Some municipalities, for example, may restrict you from permanently modifying older facilities with historical value. This could limit the drilling of holes in walls during the installation of LAN cabling and network outlets. In this situation, a wireless LAN might be the only solution. Right-of-way restrictions within cities and counties may also block the digging of trenches in the ground to lay optical fiber for the interconnection of networked sites.

#### **1.5.3 Reduced Installation Time**

The installation of cabling is often a time-consuming activity. For LANs, installers must pull twisted-pair wires above the ceiling and drop cables through walls to network outlets that they must affix to the wall. These tasks can take days or weeks, depending on the size of the installation. The installation of optical fiber between buildings within the same geographical area consists of digging trenches to lay the fiber or pulling the fiber through an existing conduit. You might need weeks or possibly months to receive right-of-way approvals and dig through ground and asphalt. The deployment of wireless LANs, MANs, or WANs greatly reduces the need for cable installation, making the network available for use much sooner. Thus, many countries lacking a network infrastructure have turned to wireless networking as a method of providing connectivity among computers without the expense and time associated with installing physical media.

#### 1.5.4 Increased Reliability

A problem inherent to wired networks is the downtime due to cable faults. Moisture erodes metallic conductors. These imperfect cable splices can cause signal reflections that result in unexplainable errors. The accidental cutting of cables can also bring a network down quickly. Water intrusion can also damage communications lines during storms. These problems interfere with the users' ability to utilize network resources, causing havoc for network managers. The advantage of wireless networking, then, is experiencing fewer problems because less cable is used.

#### 1.5.5 Long-term Cost Savings

Companies reorganize, resulting in the movement of people, new floor plans, office partitions, and other renovations. These changes often require re-cabling the network, incurring both labor and material costs. In some cases, the re-cabling costs of organizational changes are substantial, especially with large enterprise networks. The advantage of wireless networking is again based on the lack of cable—you can move the network connection by simply relocating an employee's PC.

# 1.6 The Future of Wireless Networks ERS/

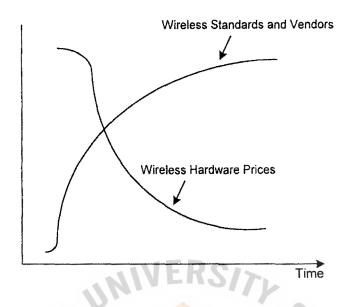

Where is wireless networking going? What will the future bring predicting what the state of this technology and its products will be five years from now, or even a year from now. The outlook for wireless networks, however, is very good. As figure 1.12 illustrates, the maturation of standards should motivate vendors to produce new wireless products and drive the prices down to levels that are much easier to justify. The presence of standards will motivate smaller companies to manufacture wireless components because they will not need to invest large sums of money in the research and development phases of the product. These investments will have already been made and embodied within the standards, which will be available to anyone interested in building wireless network components.

Figure 1.12 The future of wireless networking

In the next chapter, we introduce the concepts of the direct sequence spread spectrum and QPSK modulation technique that we use in our design. Chapter 3 presents the hardware design. A transmitter has been designed and built to perform QPSK modulation, direct sequence spread spectrum, and moved the baseband spread spectrum to IF frequency at 80 MHz. Chapter 4 is simulation and measurement. We design a simulation circuit and compare with the measurement result.

#### CHAPTER 2. THEORY OF DSSS AND QPSK

#### 2.1 Spread Spectrum

Over the last six or seven years a new commercial marketplace has been emerging. Called spread spectrum, this field covers the art of secure digital communications that is now being exploited for commercial and industrial purposes. In the next five years hardly anyone will escape being involved, in some way, with spread spectrum communications. Applications for commercial spread spectrum range from "wireless" LAN's (computer to computer local area networks), to integrated bar code scanner/palmtop computer/radio modem devices for warehousing, to digital dispatch, to digital cellular telephone communications, to "information society" city/area/state or country wide networks for passing faxes, computer data, email, or multimedia data.

#### 2.1.1 How Spread Spectrum Works

Spread Spectrum uses wide band, noise-like signals. Because Spread Spectrum signals are noise-like, they are hard to detect. Spread Spectrum signals are also hard to intercept or demodulate. Further, Spread Spectrum signals are harder to jam (interfere with) than narrowband signals. These low probability of intercept and anti-jam features are why the military has used Spread Spectrum for so many years. Spread signals are intentionally made to be much wider band than the information they are carrying to make them more noise-like. Spread Spectrum signals use fast codes that run many times the information bandwidth or data rate. These special "Spreading" codes are called "Pseudo Random" or "Pseudo Noise" codes.

Spread Spectrum transmitters use similar transmit power levels to narrow band transmitters. Because Spread Spectrum signals are so wide, they transmit at a much

lower spectral power density, measured in Watts per Hertz, than narrowband transmitters. This lower transmitted power density characteristic gives spread signals a big plus. Spread and narrow band signals can occupy the same band, with little or no interference. This capability is the main reason for all the interest in Spread Spectrum today.

#### 2.1.2 More Details on Spread Spectrum

Spread spectrum communication is a means of transmitting a signal over a much wider frequency bandwidth than the minimum bandwidth required to transmit the information. If radio signals could be seen as light, a spread spectrum signal would look like a floodlight whereas a narrow-band signal would look like a spotlight of equal intensity. Unlike a narrow-band signal where the majority of the energy transmitted is concentrated at its center frequency, a spread spectrum signal uses an equal amount of energy but spreads this energy over a wider frequency band around its center frequency. This spreading process makes the signal virtually undetectable by normal receiving techniques. A spread spectrum receiver performs the opposite function, "de-spreading" the signal. Spreading a signal reduces interference because when the spread spectrum signal is compressed to its original bandwidth, the interfering noise remains spread over a large bandwidth.

A true spread spectrum system must meet two criterias:

- The transmitted bandwidth must be at least ten times the information bandwidth being sent.

- A function other than the information being sent is used to retrieve the resulting modulated RF bandwidth.

Many modulation schemes are used to generate a spread spectrum signal. The most common types are Direct Sequence, Frequency Hopping, Pulsed FM, and Time Hopping modulation. All spread spectrum modulation types use a pseudo-random binary word known as a "code sequence" to modulate the signal carrier frequency. A spread signal not possessing the exact code sequence will appear as wideband noise. This effect is the basis for what is known as "Code Division Multiple Access" or CDMA, which allows multiple code sequences or "channels" to be used simultaneously, each operating in the same frequency band. Spread spectrum signals can share frequency bands without dividing the signals into individual frequency channels as in narrowband signals.

The ability of a receiver to compress a spread signal to its original form is known as the "Process Gain." This parameter is defined as the difference between the signal-tonoise (in dB) of the transmitted bandwidth to the signal-to-noise (in dB) of the information bandwidth. Process gain can also be thought of as an improvement or "gain" realized when the spread signal is despread back into the original signal, and can be estimated by the ratio of spread signal bandwidth to the despread signal bandwidth.

$$G_{P} = \frac{BW_{RF}}{BW_{Info}}$$

In addition, the process gain provides "noise rejection" because all signals that do not match up with the receiver code sequence do not get increased by this gain. In fact, an interfering signal will actually be reduced. The amount of interference a system is able to withstand while producing the required output signal-to-noise ratio is known as the "jamming margin". This jamming margin is the difference between the system process gain and the sum of all system implementation losses with the output signal-tonoise ratio. The system is not expected to operate with interference greater than this jamming margin. However, in a supervised security system, if a loss of signal did occur it would not cause a false alarm. Instead, a trouble signal would be generated.

One way to look at spread spectrum is that it trades a wider signal bandwidth for better signal to noise ratio. Frequency hop and direct sequence are well-known techniques today. The following paragraphs will describe each of these common techniques in a little more detail and show that pseudo noise code techniques provide the common thread through all spread spectrum types.

# 2.1.3 Direst Sequence Spread Spectrum

Direct sequence spread spectrum combines a data signal at the sending station with a higher data rate bit sequence, which many refer to as a chipping code (also known as processing gain). A high processing gain increases the signal's resistance to interference. The minimum linear processing gain that the FCC allows is 10, and most products operate under 20. The IEEE 802.11 Working Group has set their minimum processing gain requirements at 11.

Figure 2.1 shows an example of the operation of direct sequence spread spectrum. A chipping code is assigned to represent logic "one" and "zero" data bits. As the data stream is transmitted, the corresponding code is sent. For example, the transmission of a data bit equal to "one" would result in sequence 00010011100 being sent.

# St. Gabriel's Library, Au

| Chipping Code: 0 = 11101100011<br>1 = 00010011100 |             |             |                       |  |  |  |

|---------------------------------------------------|-------------|-------------|-----------------------|--|--|--|

| Data Stream: 101                                  |             |             |                       |  |  |  |

| Transmitted Seque                                 | ence:       |             |                       |  |  |  |

| 00010011100                                       | 11101100011 | 00010011100 | •<br>•<br>•<br>•<br>• |  |  |  |

| 1                                                 | 0           | 1           |                       |  |  |  |

Figure 2.1 The operation of direct sequence spread spectrum.

Many direct sequence products on the market utilize more than one channel in the same area; the number of channels available, however, is limited. With direct sequence, many products operate on separate channels by slicing the frequency band into non-overlapping frequency channels. This results in the potential for several separate networks to operate without interfering with each other. To leave enough bandwidth for moderate to high data rates, however, there can only be a few channels. Proxim's ProxLink and RangeLAN product families, for example, use direct sequence technology in the 902-928 MHz frequency band. ProxLink incorporates seven different channels, and RangeLAN uses three channels.

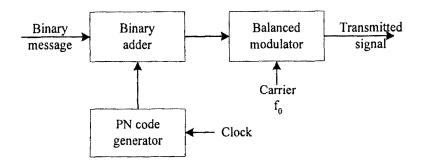

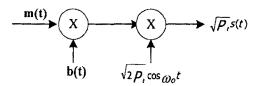

Terms direct sequence and pseudonoise are used interchangeably here and no distinction is made between them. A typical direct-sequence transmitter is illustrated in figure 2.2. Note that it contains a PN code generator that generates the pseudonoise sequence. The binary output of this code generator is added, modulo 2, to the binary message, and sum is then used to modulate a carrier.

Figure 2.2 Direct-sequence transmitter.

An important parameter that is sometimes useful in specifying the performance of a spread-spectrum signal in the presence of interference is known as the processing gain. This processing gain, PG, is the frequently defined as the ratio of the signal bandwidth to the message bandwidth.

$$PG = \frac{B_s}{B_m} = \frac{2t_m}{t_1}$$

The signal bandwidth is  $2/t_1$  and the bandwidth of the message  $B_m$  is simply  $1/t_m$  because it is customary to use only the positive frequency portion of the spectrum in defining bandwidth.

Figure 2.3 Generation of PN signals.

In figure 2.3 indicates the operations that must be performed in generating a PN signal. The quantities in this figure are defined as; m(t)=binary message, b(t)=PN code, s(t)=normalized signal.

$$s(t) = \sqrt{2}m(t)b(t)\cos \omega_o t$$

Note that the binary signals m(t) and b(t) are simply multiplied to create a new binary signal that phase-modulates the carrier. This is done by multiplying the new binary signal with a steady-state sinusoid to produce the output signal s(t). The spectral density of s(t) was obtained by assuming m(t) and b(t) to be random quantities and taking the Fourier transform of the auto-correlation function. The result is

$$S_{s}(f) = \frac{t_{1}}{2} \left\{ \left[ \frac{\sin \pi (f - f_{0})t_{1}}{\pi (f - f_{0})t_{1}} \right]^{2} + \left[ \frac{\sin \pi (f + f_{0})t_{1}}{\pi (f + f_{0})t_{1}} \right]^{2} \right\}$$

#### 2.1.4 Frequency Hopping Spread Spectrum

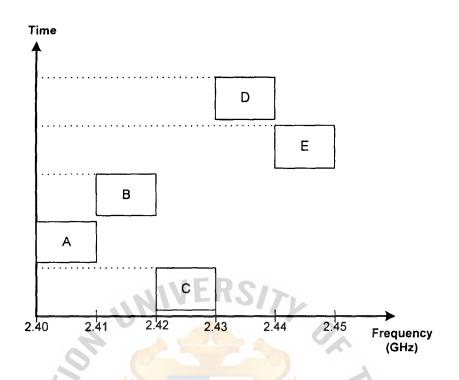

Frequency hopping works very much like its name implies. It takes the data signal and modulates it with a carrier signal that hops from frequency-to-frequency as a function of time over a wide band of frequencies (see figure 16). A frequency hopping radio, for example, will hop the carrier frequency over the 2.4 GHz frequency band between 2.4 GHz and 2.483 GHz. A hopping code determines the frequencies the radio will transmit and in which order. To properly receive the signal, the receiver must be set to the same hopping code and "listen" to the incoming signal at the right time and correct frequency. FCC regulations require manufacturers to use 75 or more frequencies per transmission channel with a maximum dwell time (time at a particular frequency) of 400 ms. If the radio encounters interference on one frequency, then the radio will retransmit the signal on a subsequent hop on another frequency.

Figure 2.4 A frequency hopping spread spectrum.

The frequency hopping technique reduces interference because the propagation from narrow band systems will only affect the spread spectrum signal when it is using the frequency of the narrow band signal. Thus, the aggregate interference will be very low, resulting in little or no bit errors. Operating radios can use spread spectrum within the same frequency band and not interfere, assuming they each use a different hopping pattern. While one radio is transmitting at one particular frequency, the other radio uses a different frequency. A set of hopping codes that never use the same frequencies at the same time is considered orthogonal. Some vendors allow the user to choose the channel (a particular hopping code) through software that the radio will operate on, all users within the same local network, however, have to use the same code. This does give you the ability, though, to have wireless LANs within close proximity to each other operate within the same band and not interfere with each other, as long as you assign them orthogonal hopping codes. The FCC's requirement for the number of different transmission frequencies allows frequency-hopping radios to have many non-interfering channels.

#### 2.1.5 Direct Sequence vs. Frequency Hopping

The direct sequence and frequency hopping are the most commonly used methods for the spread spectrum technology. Although the basic idea is the same, these two methods have many distinctive characteristics that result in complete different radio performances. The user should, based on his need and application, determine which method is best for him.

#### 2.1.5.1 The Basics

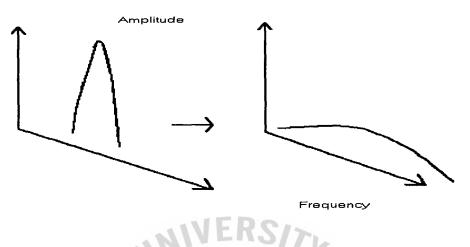

The carrier of the direct sequence radio stays at a fixed frequency. The narrow band informations are spread out into a much larger (at least 10 times) bandwidth by using a pseudo-random chip sequence. The generation of the direct sequence spread spectrum signal (spreading) can be shown as follows, E1960

## St. Gabriel's Library, Au

#### Spreading

Figure 2.5 Spreading of direct sequence signal

Please note that in the above figure, the narrowband signal and the spread spectrum signal both use the same amount of transmit power and carry the same information. However, the power density of the spread spectrum signal is much lower than the narrowband signal. As a result, it is more difficult to detect the presence of the spread spectrum signal. The power density is the amount of power over a certain frequency. In this case, the narrowband signal's power density is 10 times higher than the spread spectrum signal, assuming the spread ratio is 10.

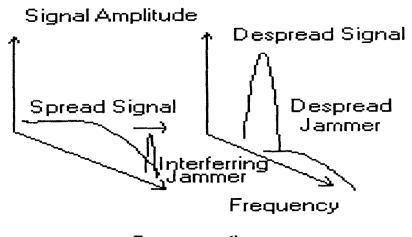

At the receiving end, the spread spectrum signal is despread to generate the original narrowband signal as shown in the following figure,

32

Despreading

Figure 2.6 Despreading of direct sequence signal

If there is an interference jammer in the same band, it will spread out during the despreading. As a result, its impact is greatly reduced. This is the way that the direct sequence spread spectrum radio fights the interference. It spreads out the offending jammer by the spreading factor, which are at least 10. In other words, the offending jammer's amplitude is greatly reduced by at least 90%.

The frequencies hopping achieve the same result by using different carrier frequency at different time. Its carrier will hop around within the band so that hopefully it will avoid the jammer at some frequencies. The frequency hopper is more popular and is the only way to survive in the 2.45 GHz band because of the leakages from the microwave oven (from 2.4 to 2.5 GHz) sometimes exceeds 10W! The need for frequency hopper in 915 MHz band is not there because there is no legal big jammer in this frequency. The frequency hopping can be shown as the following figure,

Frequency Hopping

Figure 2.7 Frequency hopping signal

#### 2.1.5.2 Comparisons

- The frequency hopping technique does not spread the signal, as a result, there is no processing gain. The processing gain is the increase in power density when the signal is despread and it will improve the received signal's S/N ratio. In other words, the frequency hopper needs to put out more power in order to have the same S/N as a direct sequence radio.

- The frequency hopper is also more difficult to synchronize the receiver to the transmitter because both the time and frequency need to be in tune. While in a direct sequence radio, only the timing of the chips needs to be synchronized. The frequency hopper will need to spend more time to search the signal and lock to it. As a result, the latency time is usually longer. While a direct sequence radio can lock in the chip sequence in just a few bits.

- Usually, to make the initial synchronization possible, the frequency hopper will park at a fixed frequency before hopping or communications begin. If the jammer happens to locate at the same frequency as the parking frequency, the hopper will not be able to hop at all! And once it hops, it will be very difficult, if not impossible to re-synchronize if the receiver ever lost the sync.

- The hopper is usually cost more and more complicated than the direct sequence radio because it needs extra hopping and synchronizing circuits to implement the synchronization algorithm.

- The frequency hopper, however, is better than the direct sequence radio when dealing with multipath. This is because that the hopper does not stay at the same frequency and a null at one frequency is usually not a null at another frequency if it is not too close to the original frequency. So a hopper can usually survive the multipath better than direct sequence radio.

- The frequency hopper can usually carry more data than the direct sequence radio because the signal is narrowband.

- In the 915 MHz band, the hopper does not have any edge over the direct sequence in dealing the interference because it has the same effect on both systems. One reduces its impact by avoiding the jammer and the other by spreading or diluting offending jammer. The net effect is the same.